|

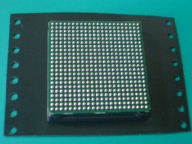

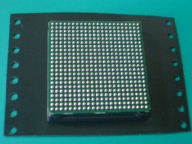

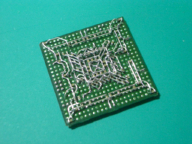

使用するFPGA

AlteraのCycloneIII、EP3C120F484です。

パッケージサイズは23mm×23mm。

Digi-Keyにて46,446円でした。

万が一壊しでもしたら(汗)・・・経済的、精神的ダメージは計り知れません。

でも予算の都合により、これをユニバーサル基板に手配線で動かすことにします。

|

|

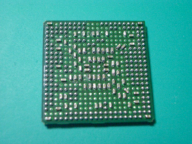

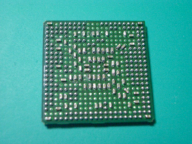

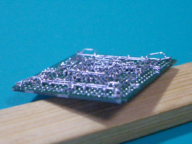

FPGA裏面

1mm間隔でびっしりと並んだ、484個のはんだボール。

これが今回の戦場です。

|

|

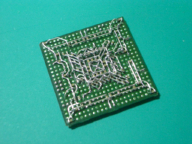

パスコンを実装

電源ピンとグランドピンは概ねきれいに隣接して配置されているので、それらを繋ぐようにパスコンを直接実装します。

1mmピッチなので1005のコンデンサがちょうどぴったりです。

|

|

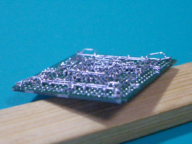

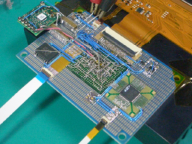

電源系の配線

主な電源とグランドを配線したところ。

電源は1.2V、2.5V、3.3Vの3系統ですが、特にコア電源の1.2Vは電流が大きいので要注意です。

写真では見えませんが、何個かのプルアップ抵抗も直接実装してあります。

こういう“無責任でバカバカしく難しい”配線作業は本当に楽しいです。

|

|

配線の様子

配線は複雑に立体交差しています。

さながらジャングルジムのよう。

通電中にショートしたら終わりです。慎重に、慎重に・・・。

|

|

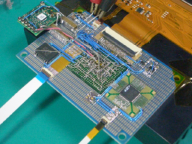

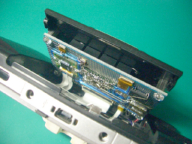

基板製作

FPGAを基板に組み込み、さらに主な周辺回路を実装したところ。

基板は秋月の表面実装用ユニバーサル基板です。その中央部分にFPGAがちょうど入る角穴を開けて落とし込み、周辺回路と接続しています。FPGAを角穴に落とし込んでいるのは、基板下のヒートシンクとFPGAを熱結合させるためです。

左下に延びている2本のFFCは開発環境との接続用です。太い方はJTAG、細い方はマイコン用です。

|

|

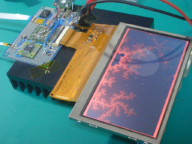

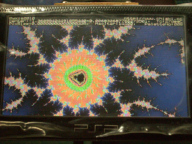

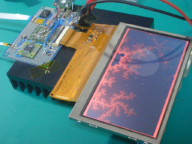

動作確認

バラックで取り急ぎ動作が確認できた記念の1枚です。

液晶パネルには初期型のPSP(PSP1000)用として販売されているものを使いました。

1個のFPGAの中に、演算回路と合わせてグラフィックRAM(フレームバッファ)、カラーパレットテーブル、キャラクタRAM、キャラクタジェネレータ、液晶用制御信号生成回路なども入れてあります。ですのでFPGA以外の主な部品は、FPGAのコンフィグレーションROMとマンマシンインターフェース処理用マイコン、電源類しかありません。

|

|

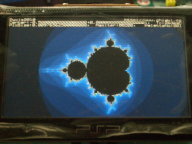

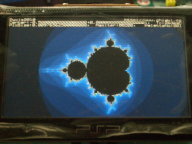

実行速度の確認

マンデルブロ集合の全体像を表示してみました。

横480ピクセル×縦256ピクセル、実軸上の座標範囲(-2.5, +1.5)、最大反復回数256回です。

計算時間は5.84msecでした。

|

|

電源の実装準備

FPGAのコア電源(1.2V)には市販のPOL用DC/DCコンバータ(BellnixのBSV-3.3S8R0M)を使用しました。

写真は電源実装前の基板の裏側です。電源はFPGA左側のスペースに実装します。

この基板は裏側が全面ベタなので、それを電源の放熱用として有効活用します。FPGAの左に見える銅色の長方形は、電源の放熱用パッドをはんだ付けするためにレジストを削り取った部分です。

|

|

電源の実装とFPGA用ヒートシンク

電源の放熱用パッドをベタにしっかりとはんだ付けして固定し、スズメッキ線を使って基板表側と入出力を最短で接続します。電源の周囲が緑色なのは、絶縁確保のために電源の下一帯にカプトンテープを貼ってあるからです。

さらにFPGA用のヒートシンクを貼り付けて、基板の裏側は完成です。

強制空冷の際に冷却風が電源の方へ流れるように、ヒートシンクのフィンは横向きにしておきます。

|

|

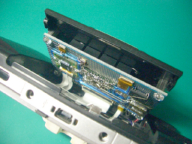

PSPへの組み込み準備(1)

Pyxis 2010のケースはPSPです。

壊れたPSP1000をオークションで安く調達し、改造して組み込みます。

写真は液晶パネルと板金フレームを外した様子です。

|

|

PSPへの組み込み準備(2)

メイン基板は写真の通りに惜しげもなく二分し、右側の細い方だけを使います。

こうしたのは次の3つの理由から。ひとつめは、ケースを元通り組み立てるためにはネジ部分の基板が必要なこと。2つめは、本体左側の方向スイッチやアナログスティックを構造的に受けるものとして、その部分の基板が必要なこと。3つめは、基板の剛性が全体の"しっかり感"に欠かせないこと。メイン基板は"かなりの"多層板なので剛性が高く、これだけ細く切ってしまっても相応の効果が期待できます。

|

|

PSPへの組み込み(1) -放熱

いよいよPSPへ組み込みます。

UMDを取り外し、板金部品やプラスチックケースの一部も切り取って、できたスペースに製作した基板を納めます。秋月のユニバーサル基板はこのUMDのスペースにお誂え向き。ちょうどぴったりの寸法です。

UMDのふたには冷却用のファンを付けました。ヒートシンクとPOL電源を両方同時に強制空冷できる配置になっています。

|

|

PSPへの組み込み(2) -基板の固定

基板は本体側ではなく、UMDのふた側にスタッドで固定します。

秋月のユニバーサル基板に付いている四隅のねじ穴をそのまま使いました。

|

|

PSPへの組み込み(3) -基板と本体の接続

液晶パネルやスイッチ基板からは元々メイン基板と接続されていたFPCが出ていますが、それらは組み込んだ基板までは届きません。ですので、その延長も兼ねてFFCを"ごにょごにょ"っと接続します。

市販品の長さでちょうど良く接続でき、かつ繰り返しの開閉に耐えられるように、FFCの通し方や折り返しの位置を考えておきます。

|

|

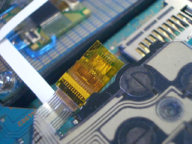

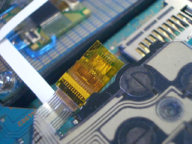

PSPへの組み込み(4) -FPCとFFCの接続

FPCとFFCを"ごにょごにょ"っと接続している部分です。

FPC用コネクタと市販の極薄エクステンション基板を介して、細い線材で両者を接続しています。ピッチは0.5mmです。さらにここで、ユニバーサル基板上での配線の都合に合わせて信号の並びを入れ替えました。

|

|

PSPへの組み込み(5) -本体裏側の処理

UMDのふたの"PSP"ロゴが入っている部分を全てくりぬくと、40mm角ファンの開口にちょうど良い丸穴になります。

基板を固定しているネジですが、座面がふた両端の曲面の部分に掛かってしまうために、リューターで平ザグリを入れてあります。

なお、この裏面はまだ仮の姿です。

|

|

PSPへの組み込み(6) -動作確認

取り急ぎ動作確認。無事に動きました。

期待通り、PSPのスイッチ類を利用した操作性は抜群です。

スクロールやズームイン、ズームアウトも思いのまま。

でもまだ完成ではないので、保護フィルムの"除幕式"はしばらく先になりそうです。

|

|

組み込み後の開発環境との接続

FPGA用とマイコン用のそれぞれの開発環境と接続している様子です。

作業をやりやすくするため、UMDのふたが通常よりも大きく開くように追加工してあります。

|

|

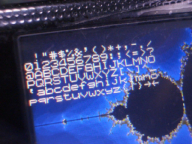

オーバレイによる文字表示

座標値などの各種情報表示用に、キャラクタジェネレータ方式による文字のオーバレイ表示ができるようにしました。

このキャラクタジェネレータとキャラクタRAMも、フレームバッファと同様にFPGA内のメモリを利用しました。小容量なので問題なくFPGA内に納まります。

|

|

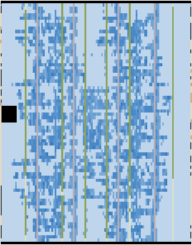

フォント作成

文字サイズは8ピクセル×8ピクセルにしてみました。行間と文字間に1ピクセルずつ空けるため、実際は7×7です。

キャラクタジェネレータのフォントデータはオリジナルで作成しました(写真)。その際にQuartusIIの"In-System Memory

Content Editor"を使ったのですが、これは超便利なツールですね。JTAG経由で実際の表示を確認しながら作業できたので、あっという間にできあがりました。

その昔、机上でフォントをデザイン→バイナリファイル作成→EPROM書き込み→結果確認、気に入らなければ殺菌灯でROM消してデータ修正を繰り返すという経験をしているので、このお手軽さはまさに天国です。良い時代になりました。

|

|

デモ画像(1) -起動画面

電源オン後、最初にタイトル「Pyxis 2010」を表示する起動画面を作ってみました。

バックライト駆動ICにPWMをかけて、スムースなフェードイン/アウトができるようにしました。

○ボタンを押すと、次の動作画面に移ります。

|

|

デモ画像(2) -動作画面

画面上部に各種ステータスを表示するようにしました。

1行目はとりあえずタイトルです。

2行目は画面中央の複素座標と、FPGAに取り付けた温度センサの検出値です。

3行目は1ピクセル分の座標幅、発散と見なす最大反復回数、パレット番号が表示されます。

|

|

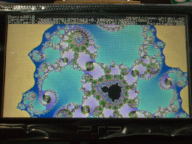

デモ画面(3) -パレット変更(1)

Mandelbrot集合のグラフィクス表示は、Z0 = 0 および各ピクセルの複素座標を C として漸化式 Zn+1 = Zn2 + C を反復計算し、その値が発散すると判定された時点での n の値に対応した色でそのピクセルを描画することで実現されます。したがってこの

n の値と色の対応付けが、出力画像の見え方を左右する重要な要素になります。

Pyxis2010にはこの対応付けのためのパレットと呼ぶ色データテーブルが組み込んであります。パレットの実装によって漸化式の計算と色付けを分離することができ、パレット変更だけで見え方を変えることができます。

現在は9種類のパレットを定義してあります。左右ボタンでいつでも切り替えられるようにしてあります。

左の写真は連続サイクリック型(全体にスムースに色が変化し、かつ周期的に同じ色パターンが繰り返されるタイプ)のパレットのひとつです。

|

|

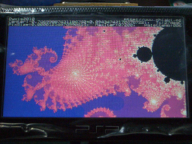

デモ画面(4) -パレット変更(2)

これは不連続サイクリック型(色の変化に不連続な箇所があり、かつ周期的に同じ色パターンが繰り返されるタイプ)のパレットです。

表示している座標範囲は上の(1)と同じです。パレットを変えるだけでこんなに見え方が変わります。

|

|

デモ画面(5) -パレット変更(3)

これは連続非サイクリック型(スムースに色が変化し、かつその変化が周期的でないタイプ)です。

Mandelbrot集合周辺部などの入り組んだ箇所でも、なめらかな色の変化が得られるパレットです。

|

|

デモ画面(6) -パレット変更(4)

これは(1)と同じ、連続サイクリック型の別のパレットです。色の変化の仕方が異なると全然印象が違ってきます。

パレットの定義は奥が深くて面白い作業です。

|

![オリジナル[ Pyxis ]](../Pyxis/Current/images/pyxisbox2_s.jpg)

![]() マンデルブロ集合についてはこちらへ

マンデルブロ集合についてはこちらへ![]() Pyxisについてはこちらへ

Pyxisについてはこちらへ![]()