このページは,Timpyシリーズでお世話になっているVLSI Solution Oy製のMP3デコーダ・チップ,VS1011のデータシートを勝手に和訳したものです.

オリジナルの文書はVS1011e Datasheet Version 1.04です.

この和訳の公開については,念のためVLSI Solution Oy社に報告してあります.

VS1053bならこちらへ  VS1053b 日本語データシート私家版

VS1053b 日本語データシート私家版

【注意】このページの内容の一部または全部を断りなく複写複製することを禁じます.

必ず事前にご連絡ください.メール・アドレスはトップ・ページにあります.Copyright (C) 2006-2008 Chiaki Nakajima.

【免責事項】この文書の内容により利用者に損害が生じたとしても著作権者は責任を負いません.

この文書の内容の正確性は保障されません.また断りなく変更される場合があります.

VS1011e - MPEG オーディオ・コーデック

【特長】

・MPEG1.0,2.0のオーディオ・レイヤIII(CBR,VBR,ABR),レイヤI,II(オプション),WAV(PCM+IMA ADPCM)をデコード可能.

・12.0MHzの外部クロックで320kbit/sのMP3を再生.

・MP1/2/3とWAVのストリーミングをサポート.

・低音(BASS)および高音(TREBLE)のコントロール.

・12〜13MHzまたは24〜26MHzの単一外部クロックで動作.

・クロック・ダブラ内蔵.

・低消費電力.

・チャンネル間で位相差のない高音質ステレオDAC.

・30Ω負荷を駆動できるステレオ・ヘッドフォン・アンプ.

・アナログ用とディジタル用に分離された2.5〜3.6Vの動作電源.

・シリアル方式のコントロールおよびデータ用インターフェース.

・スレーブ・コプロセッサとして使用可能.

・ユーザ用のコード/データRAMを5.5KiB内蔵.

・特殊なアプリケーション用のSPIフラッシュ・ブート.

・ソフトウェアと汎用I/O端子4本により新機能を追加可能.

・LQFP-48およびBGA-49パッケージは鉛フリーでRoHSに対応.

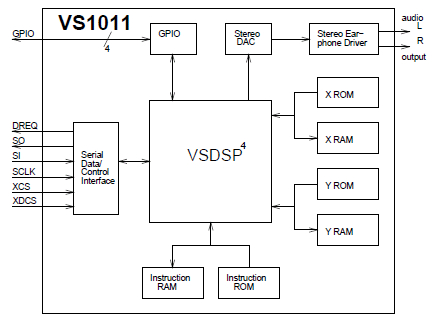

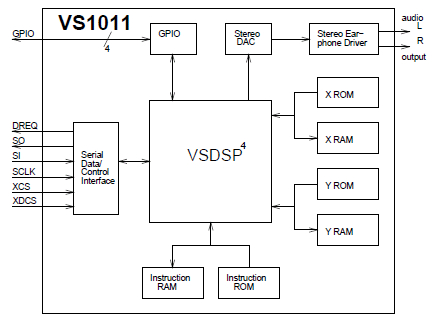

【概説】

VS1011eは単体で動作するMPEGオーディオ・デコーダ・チップです.高速かつ低消費電力のDSPコアVS_DSP4の他,ワーキング・メモリ,ユーザ・アプリケーション用の5KiBインストラクションRAMと0.5KiBデータRAM,内部コントロール用およびデータ入力用の各シリアル・インターフェース,汎用I/O端子4本,高品質の可変サンプルレート対応ステレオDAC,ヘッドフォン・アンプ,グランド・バッファを内蔵しています.

VS1011eは,スレーブとして動作するシリアル・バスを通して,オーディオ・データのビットストリームを受信します.そのビットストリームはまずデコードされ,ディジタル・ボリューム・コントロールを通った後,18ビット・オーバサンプリング・マルチビット・シグマデルタDACへと送られます.デコード処理はシリアル方式のコントロール・バスによって制御されます.さらに,基本的なデコード処理に加えて,例えばDSPエフェクトのような特定用途向けの機能をユーザRAM領域へ追加することも可能です.

【目次】

1 ライセンス

2 免責事項

3 用語の定義

4 特性および仕様

4.1 絶対最大定格

4.2 推奨動作条件

4.3 アナログ特性

4.4 消費電力

4.5 ディジタル特性

4.6 スイッチング特性 - 起動,初期化

5 パッケージと端子の説明

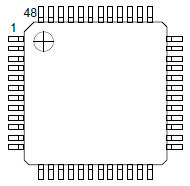

5.1 パッケージ

5.1.1 LQFP-48

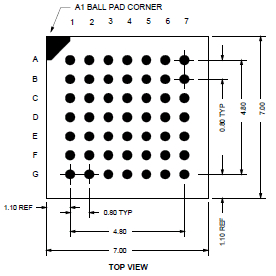

5.1.2 BGA-49

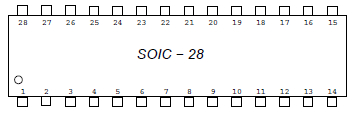

5.1.3 SOIC-28

5.2 端子の説明

5.2.1 LQFP-48,BGA-49パッケージの端子説明

5.2.2 SOIC-28パッケージの端子説明

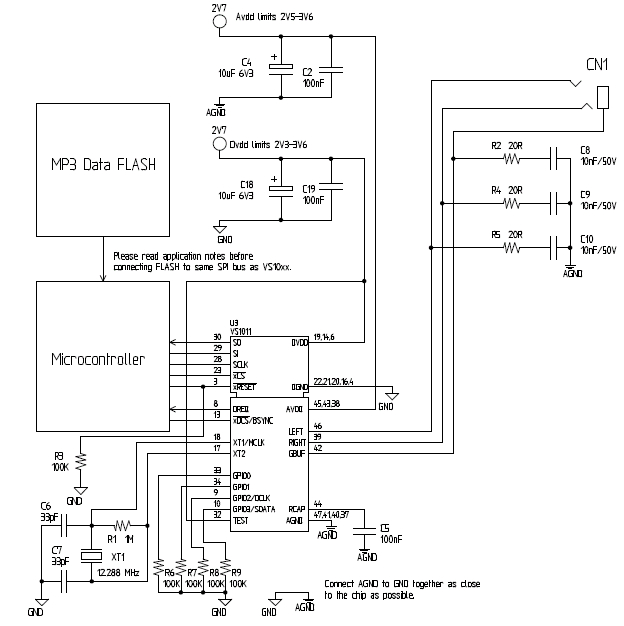

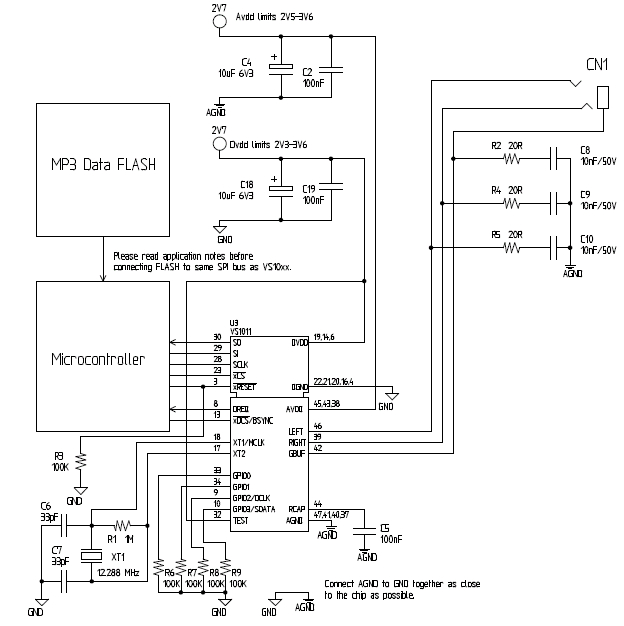

6 LQFP-48での接続図

7 SPIバス

7.1 概要

7.2 SPIバスの端子説明

7.2.1 VS1002ネイティブ・モード(Newモード)

7.2.2 VS1001互換モード

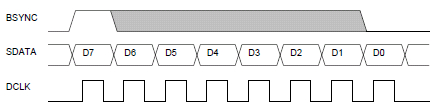

7.3 シリアル・データ・インターフェース(SDI)の通信プロトコル

7.3.1 概要

7.3.2 VS1002ネイティブ・モード(Newモード)時のSDI

7.3.3 VS1001互換モード時のSDI

7.4 データ・リクエスト端子DREQ

7.5 シリアル・コマンド・インターフェース(SCI)の通信プロトコル

7.5.1 概要

7.5.2 SCIリード

7.5.3 SCIライト

7.6 SPIタイミング・ダイアグラム

7.7 SM_SDINEWおよびSM_SDISHARED有効時のSPI動作例

7.7.1 2回のSCIライト転送

7.7.2 2回のSDIバイト転送

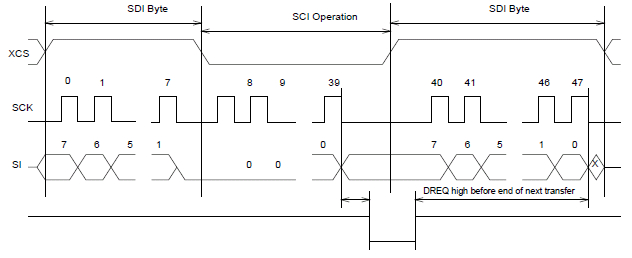

7.7.3 SCIオペレーションをはさんだ2回のSDIバイト転送

8 機能解説

8.1 主な機能

8.2 サポートされるオーディオ・コーデック

8.2.1 サポートされるMP1(MPEG レイヤI)フォーマット

8.2.2 サポートされるMP2(MPEG レイヤII)フォーマット

8.2.3 サポートされるMP3(MPEG レイヤIII)フォーマット

8.2.4 サポートされるRIFF WAVフォーマット

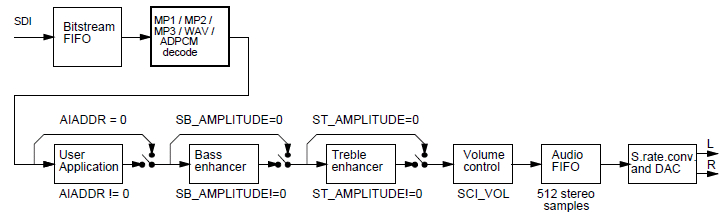

8.3 VS1011eのデータ・フロー

8.4 シリアル・データ・インターフェース(SDI)

8.5 シリアル・コントロール・インターフェース(SCI)

8.6 SCIレジスタ

8.6.1 SCI_MODE(RW)

8.6.2 SCI_STATUS(RW)

8.6.3 SCI_BASS(RW)

8.6.4 SCI_CLOCKF(RW)

8.6.5 SCI_DECODE_TIME(RW)

8.6.6 SCI_AUDATA(RW)

8.6.7 SCI_WRAM(RW)

8.6.8 SCI_WRAMADDR(RW)

8.6.9 SCI_HDAT0およびSCI_HDAT1(R)

8.6.10 SCI_AIADDR(RW)

8.6.11 SCI_VOL(RW)

8.6.12 SCI_AICTRL[x](RW)

9 オペレーション

9.1 クロック

9.2 ハードウェア・リセット

9.3 ソフトウェア・リセット

9.4 SPIブート

9.5 プレイ/デコード

9.6 PCMデータの入力

9.7 SDIテスト

9.7.1 正弦波テスト

9.7.2 端子テスト

9.7.3 メモリ・テスト

9.7.4 SCIテスト

10 VS1011e内蔵レジスタ

10.1 本章を必要とするユーザ

10.2 プロセッサ・コア

10.3 VS1011eメモリ・マップ

10.4 SCIレジスタ

10.5 シリアル・データ・レジスタ

10.6 DACレジスタ

10.7 GPIOレジスタ

10.8 インタラプト・レジスタ

10.9 システム・ベクタ・タグ

10.9.1 AudioInt,0x20

10.9.2 SciInt,0x21

10.9.3 DataInt,0x22

10.9.4 UserCodec,0x0

10.10 システム・ベクタ関数

10.10.1 WriteIRam(),0x2

10.10.2 ReadIRam(),0x4

10.10.3 DataBytes(),0x6

10.10.4 GetDataByte(),0x8

10.10.5 GetDataWords(),0xa

11 VS1011バージョン履歴

11.1 VS1011bとVS1011eの相違点,2005-07-13

11.2 VS1011bからVS1011eへ移行する場合の確認事項,2005-07-13

12 本文書の改版履歴

12.1 VS1011e用バージョン1.04,2007-10-08

12.2 VS1011e用バージョン1.03,2005-09-05

12.3 VS1011e用バージョン1.02,2005-07-13

12.4 VS1011b用バージョン1.01,2004-11-19

12.5 VS1011b用バージョン1.00,2004-10-22

12.6 VS1011用バージョン0.71,2004-07-20

12.7 VS1011用バージョン0.70,2004-05-13

12.8 VS1011用バージョン0.62,2004-03-24

13 連絡先

【図一覧】

1 LQFP-48のピン配置

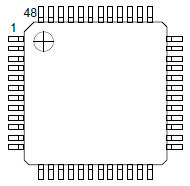

2 BGA-49のピン配置

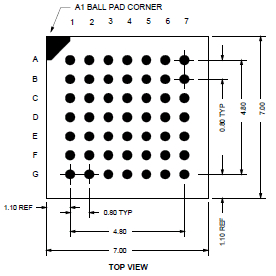

3 SOIC-28のピン配置

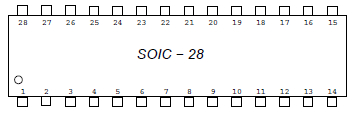

4 LQFP-48での標準接続図

5 BSYNC信号 - 1バイト転送時

6 BSYNC信号 - 2バイト転送時

7 SCIワード・リード

8 SCIワード・ライト

9 SPIタイミング・ダイアグラム

10 2回のSCIオペレーション

11 2回のSDIバイト転送

12 SCIオペレーションをはさんだ2回のSDIバイト転送

13 VS1011eのデータ・フロー

14 ユーザ用メモリ・マップ

1 ライセンス

MPEGレイヤ3オーディオ・デコーディング技術は,Fraunhofer IISおよびThomsonよりライセンス供与を受けています.

注意:もしレイヤIおよびレイヤIIのデコード機能を有効にする場合には,それらのフォーマットを使用することにより生じうる全ての特許問題について責任を負う必要があります.MPEG1.0/2.0レイヤIIIのジョイント・ライセンスの範囲は,レイヤIおよびIIに係る特許の全てを網羅していません.

2 免責事項

特性や図は変更される場合があります.

3 用語の定義

B バイト.8ビット.

b ビット.

Ki "Kibi" = 2^10 = 1024 (IEC 60027-2).

Mi "Mebi" = 2^20 = 1048576 (IEC 60027-2).

VS_DSP VLSI SolutionのDSPコア.

W ワード.VS_DSPのインストラクション・ワードは32ビット幅,データ・ワードは16ビット幅です.

4 特性および仕様

4.1 絶対最大定格

|

パラメータ

|

記号

|

Min

|

Max

|

単位

|

|

アナログ電源電圧

|

AVDD

|

-0.3

|

3.6

|

V

|

|

ディジタル電源電圧

|

DVDD

|

-0.3

|

3.6

|

V

|

|

各ディジタル出力電流

|

|

|

±50

|

mA

|

|

各ディジタル入力電圧

|

|

DGND-1.0

|

DVDD+1.0[1]

|

V

|

|

動作温度

|

|

-30

|

+85

|

℃

|

|

機能動作温度

|

|

-40

|

+95

|

℃

|

|

保存温度

|

|

-65

|

+150

|

℃

|

[1] 3.6Vを超えてはいけません.

4.2 推奨動作条件

|

パラメータ

|

記号

|

Min

|

Typ

|

Max

|

単位

|

|

動作周囲温度

|

|

-40

|

|

+85

|

℃

|

|

アナログおよびディジタル・グランド[1]

|

AGND DGND

|

|

0.0

|

|

V

|

|

アナログ電源電圧

|

AVDD

|

2.5

|

2.7

|

3.6

|

V

|

|

ディジタル電源電圧

|

DVDD

|

2.3

|

2.5

|

3.6

|

V

|

|

クロック入力周波数

|

XTALI

|

24

|

24.576

|

26

|

MHz

|

|

クロック入力周波数(クロック・ダブラ使用時)

|

XTALI

|

12

|

12.288

|

13

|

MHz

|

|

内部クロック周波数

|

CLKI

|

24[2]

|

24.576

|

26

|

MHz

|

|

マスタ・クロック・デューティ比

|

|

40

|

50

|

60

|

%

|

[1] ラッチアップ耐性向上のため,両者はできるだけデバイスの近くにて接続してください.

[2] 正規の速度で再生できるサンプル・レートの最大値はCLKI/512です.

したがって,例えばCLKIが24MHzの場合には,サンプル・レート48kHzのデータの再生音は2.5%音程がずれます.

4.3 アナログ特性

別途規定がない限り:AVDD=2.5〜3.6V,DVDD=2.3〜3.6V,TA=-40〜+85℃,XTALI=12〜13MHz,内蔵クロック・ダブラ有効.

DACの評価は1307.894Hzのフルスケール正弦波出力時,測定バンド幅20〜20000Hz,アナログ出力負荷:LEFT-GBUF間30Ω,RIGHT-GBUF間30Ω.

|

パラメータ

|

記号

|

Min

|

Typ

|

Max

|

単位

|

|

DAC分解能

|

|

|

18

|

|

ビット

|

|

全高調波歪み

|

THD

|

|

0.1

|

0.2

|

%

|

|

ダイナミック・レンジ(DAC非ミュート,Aウェイト)

|

IDR

|

|

90

|

|

dB

|

|

S/N比(フルスケール信号)

|

SNR

|

70

|

85

|

|

dB

|

|

チャンネル間分離(クロス・トーク)

|

|

50

|

75

|

|

dB

|

|

チャンネル間分離(クロス・トーク),GBUF使用時

|

|

|

40

|

|

dB

|

|

チャンネル間ゲイン誤差

|

|

-0.5

|

|

0.5

|

dB

|

|

周波数特性

|

|

-0.1

|

|

0.1

|

dB

|

|

フルスケール出力電圧(ピーク-ピーク値)

|

|

1.4

|

1.6[1]

|

2.0

|

Vpp

|

|

リニア位相からの位相偏移

|

|

|

|

5

|

°

|

|

アナログ出力負荷抵抗

|

AOLR

|

16

|

30[2]

|

|

Ω

|

|

アナログ出力負荷容量

|

|

|

|

100

|

pF

|

[1] モノラル差動出力形式ならば3.2V得られます.

[2] AOLRはこの値より小さくできますが,歪み特性に関して標準的な性能が得られなくなります.

4.4 消費電力

平均電流の測定はMPEG1.0 レイヤIII 128kbit/sサンプルおよび生成正弦波時,フル・ボリューム,XTALI=12.288MHz,内蔵クロック・ダブラ有効,DVDD=2.5V,AVDD=2.7V.

|

パラメータ

|

Min

|

Typ

|

Max

|

単位

|

|

AVDD消費電流(リセット時)

|

|

0.5

|

30

|

μA

|

|

DVDD消費電流(リセット時)

|

|

1

|

30

|

μA

|

|

AVDD消費電流(正弦波テスト時,30Ω)

|

|

20

|

|

mA

|

|

AVDD消費電流(正弦波テスト時,30Ω+GBUF)

|

|

39

|

50

|

mA

|

|

DVDD消費電流(正弦波テスト時)

|

|

8

|

17

|

mA

|

|

AVDD消費電流(無負荷時)

|

|

6

|

|

mA

|

|

AVDD消費電流(負荷30Ω時)

|

|

10

|

|

mA

|

|

AVDD消費電流(30Ω+GBUF時)

|

|

16

|

|

mA

|

|

DVDD消費電流

|

|

16

|

|

mA

|

4.5 ディジタル特性

|

パラメータ

|

記号

|

Min

|

Typ

|

Max

|

単位

|

|

"H"レベル入力電圧

|

|

0.7×DVDD

|

|

DVDD+0.3[1]

|

V

|

|

"L"レベル入力電圧

|

|

-0.2

|

|

0.3×DVDD

|

V

|

|

"H"レベル出力電圧(Io=-2.0mA)

|

|

0.7×DVDD

|

|

|

V

|

|

"L"レベル出力電圧(Io=2.0mA)

|

|

|

|

0.3×DVDD

|

V

|

|

入力リーク電流

|

|

-1.0

|

|

1.0

|

μA

|

|

SPI入力クロック周波数[2]

|

|

|

|

CLKI/6

|

MHz

|

|

全出力端子立ち上がり時間(負荷容量=50pF)

|

|

|

|

50

|

ns

|

[1] 3.6Vを超えてはいけません.

[2] この値はSCIリードに適用されます.SCIライトおよびSDIライトではCLKI/4です.

4.6 スイッチング特性 - 起動,初期化

|

パラメータ

|

記号

|

Min

|

Max

|

単位

|

|

XRESETアクティブ時間

|

|

2

|

|

XTALI

|

|

XRESETインアクティブからソフトウェア・レディまでの時間

|

|

|

50000[1]

|

XTALI

|

|

パワー・オン・リセット時のDVDD立上り時間

|

|

10

|

|

V/s

|

[1] 初期化が完了するとDREQが"H"になります.それまではデータ,コマンドともに何も送信しないでください.

5 パッケージと端子の説明

5.1 パッケージ

LQFP-48とBGA-49はともに鉛フリー,RoHS対応のパッケージです.RoHSとは"Directive 2002/95/EC

on the restriction of the use of certain hazardous substances in electrical

and electronic equipment"の短縮形です.

SOIC-28についてはVS1011eから鉛フリーのRoHS対応パッケージになっています.

5.1.1 LQFP-48

|

図1 LQFP-48のピン配置

|

LQFP-48パッケージの外形寸法はhttp://www.vlsi.fiにあります.

5.1.2 BGA-49

|

図2 BGA-49のピン配置

|

BGA-49パッケージの外形寸法はhttp://www.vlsi.fiにあります.

5.1.3 SOIC-28

|

図3 SOIC-28のピン配置

|

SOIC-28パッケージの外形寸法はhttp://www.vlsi.fiにあります.

5.2 端子の説明

5.2.1 LQFP-48,BGA-49パッケージの端子説明

|

ピン名称

|

LQFP-48

ピン番号

|

BGA-49

ピン番号

|

タイプ

|

機能

|

|

XRESET

|

3

|

B1

|

DI

|

アクティブ"L"の非同期リセット入力.シュミット・トリガ

|

|

DGND0

|

4

|

D2

|

PWR

|

ディジタル・グランド

|

|

DVDD0

|

6

|

D3

|

PWR

|

ディジタル電源

|

|

DREQ

|

8

|

E2

|

DO

|

入力バスのデータ・リクエスト

|

|

GPIO2[2]/DCLK[1]

|

9

|

E1

|

DI

|

汎用入出力2/シリアル入力データ・クロック

|

|

GPIO3[2]/SDATA[1]

|

10

|

F2

|

DI

|

汎用入出力3/シリアル・データ入力

|

|

XDCS[4]/BSYNC[1]

|

13

|

E3

|

DI

|

データ用チップ・セレクト/バイト同期.不使用ならDVDDへ接続すること

|

|

DVDD1

|

14

|

F3

|

PWR

|

ディジタル電源

|

|

DGND1

|

16

|

F4

|

PWR

|

ディジタル・グランド

|

|

XTALO

|

17

|

G3

|

AO

|

クリスタル用出力

|

|

XTALI

|

18

|

E4

|

AI

|

クリスタル用入力

|

|

DVDD2

|

19

|

G4

|

PWR

|

ディジタル電源

|

|

DGND2

|

20

|

F5

|

PWR

|

ディジタル・グランド.(BGA-49の場合DGND2,3,4は互いに接続すること)

|

|

DGND3

|

21

|

G5

|

PWR

|

ディジタル・グランド

|

|

DGND4

|

22

|

F6

|

PWR

|

ディジタル・グランド

|

|

XCS[4]

|

23

|

G6

|

DI

|

チップ・セレクト入力.(アクティブ"L")

|

|

SCLK[2]

|

28

|

D6

|

DI

|

シリアル・バス用クロック

|

|

SI[2]

|

29

|

E7

|

DI

|

シリアル入力

|

|

SO

|

30

|

D5

|

DO3

|

シリアル出力.XRESETに関係なく,XCS=0のときアクティブになる

|

|

TEST

|

32

|

C6

|

DI

|

テスト用予約端子.DVDDへ接続すること

|

|

GPIO0/SPIBOOT[2,3]

|

33

|

C7

|

DIO

|

汎用入出力0.100KΩでプルダウンすること

|

|

GPIO1[2]

|

34

|

B6

|

DIO

|

汎用入出力1

|

|

AGND0

|

37

|

C5

|

PWR

|

アナログ・グランド.ロー・ノイズ・リファレンス端子

|

|

AVDD0

|

38

|

B5

|

PWR

|

アナログ電源

|

|

RIGHT

|

39

|

A6

|

AO

|

右チャンネル出力

|

|

AGND1

|

40

|

B4

|

PWR

|

アナログ・グランド

|

|

AGND2

|

41

|

A5

|

PWR

|

アナログ・グランド

|

|

GBUF

|

42

|

C4

|

AO

|

グランド・バッファ

|

|

AVDD1

|

43

|

A4

|

PWR

|

アナログ電源

|

|

RCAP

|

44

|

B3

|

AIO

|

リファレンス電圧用フィルタ・コンデンサ接続端子

|

|

AVDD2

|

45

|

A3

|

PWR

|

アナログ電源

|

|

LEFT

|

46

|

B2

|

AO

|

左チャンネル出力

|

|

AGND3

|

47

|

A2

|

PWR

|

アナログ・グランド

|

[1] Newモードの場合は"/"の左側の機能が有効になり,互換モードでは右側の機能が有効になります.

[2] 使用しない場合は100KΩでプルダウンして下さい.

[3] 100KΩでプルダウンして下さい.もしプルアップすると,SPIブート機能が有効になります.詳細は9.4項を参照してください.

[4] 使用しない場合は100KΩでプルアップして下さい.

ピンのタイプ

|

タイプ

|

説明

|

|

DI

|

CMOSディジタル入力

|

|

DO

|

CMOSディジタル出力

|

|

DIO

|

ディジタル入出力

|

|

DO3

|

CMOSトライステート・ディジタル出力

|

|

AI

|

アナログ入力

|

|

AO

|

アナログ出力

|

|

AIO

|

アナログ入出力

|

|

PWR

|

電源端子

|

BGA-49パッケージの場合,次の端子は空き端子とする:A1,A7,B7,C1,C2,C3,D1,D4,D7,E5,E6,F1,F7,G1,G2,G7.

LQFP-48パッケージの場合,次の端子は空き端子とする:1,2,5,7,11,12,15,24,25,26,27,31,35,36,48.

5.2.2 SOIC-28パッケージの端子説明

|

ピン名称

|

SOIC-28

ピン番号

|

タイプ

|

機能

|

|

DREQ

|

1

|

DO

|

入力バスのデータ・リクエスト

|

|

GPIO2[2]/DCLK[1]

|

2

|

DIO

|

汎用入出力2/シリアル入力データ・クロック

|

|

GPIO3[2]/SDATA[1]

|

3

|

DI

|

汎用入出力3/シリアル・データ入力

|

|

XDCS[4]/BSYNC[1]

|

4

|

DI

|

バイト同期信号

|

|

DVDD1

|

5

|

PWR

|

ディジタル電源

|

|

DGND1

|

6

|

PWR

|

ディジタル・グランド

|

|

XTALO

|

7

|

CLK

|

クリスタル用出力

|

|

XTALI

|

8

|

CLK

|

クリスタル用入力

|

|

DVDD2

|

9

|

PWR

|

ディジタル電源

|

|

DGND2

|

10

|

PWR

|

ディジタル・グランド

|

|

XCS[4]

|

11

|

DI

|

チップ・セレクト入力.(アクティブ"L")

|

|

SCLK[2]

|

12

|

DI

|

シリアル・バス用クロック

|

|

SI[2]

|

13

|

DI

|

シリアル入力

|

|

SO

|

14

|

DO3

|

シリアル出力.XRESETに関係なく,XCS=0のときアクティブになる

|

|

TEST

|

15

|

DI

|

テスト用予約端子.DVDDへ接続すること

|

|

GPIO0/SPIBOOT[2,3]

|

16

|

DIO

|

汎用入出力0.100KΩでプルダウンすること

|

|

GPIO1[2]

|

17

|

DIO

|

汎用入出力1

|

|

AGND0

|

18

|

PWR

|

アナログ・グランド

|

|

AVDD0

|

19

|

PWR

|

アナログ電源

|

|

RIGHT

|

20

|

AO

|

右チャンネル出力

|

|

AGND2

|

21

|

PWR

|

アナログ・グランド

|

|

RCAP

|

22

|

AIO

|

リファレンス電圧用フィルタ・コンデンサ接続端子

|

|

AVDD2

|

23

|

PWR

|

アナログ電源

|

|

LEFT

|

24

|

AO

|

左チャンネル出力

|

|

AGND3

|

25

|

PWR

|

アナログ・グランド

|

|

XRESET

|

26

|

DI

|

アクティブ"L"の非同期リセット入力

|

|

DGND0

|

27

|

PWR

|

ディジタル・グランド

|

|

DVDD0

|

28

|

PWR

|

ディジタル電源

|

[1] Newモードの場合は"/"の左側の機能が有効になり,互換モードでは右側の機能が有効になります.

[2] 使用しない場合は100KΩでプルダウンして下さい.

[3] 100KΩでプルダウンして下さい.もしプルアップすると,SPIブート機能が有効になります.詳細は9.4項を参照してください.

[4] 使用しない場合は100KΩでプルアップして下さい.

ピンのタイプ

|

タイプ

|

説明

|

|

DI

|

CMOSディジタル入力

|

|

DO

|

CMOSディジタル出力

|

|

DIO

|

ディジタル入出力

|

|

DO3

|

CMOSトライステート・ディジタル出力

|

|

AI

|

アナログ入力

|

|

AO

|

アナログ出力

|

|

AIO

|

アナログ入出力

|

|

PWR

|

電源端子

|

6 LQFP-48での接続図

|

図4 LQFP-48での標準接続図

|

グランド・バッファGBUFは,ヘッドフォンのコモン電圧(1.23V)として使用できます.その場合は出力ラインに必要な直流カット用大容量コンデンサを省略できるため,VS1011eのオーディオ出力端子とヘッドフォン・コネクタとの直結が可能になります.

一方GBUFを使用しない場合には,負荷抵抗に応じた容量(1〜100uF)のコンデンサを,LEFTおよびRIGHT出力に接続する必要があります.

注意:この回路図はSM_SDINEWが有効の場合です(8.6.1項を参照).さらにSM_SDISHAREも使用する場合には,xDCSをプルアップしてください(7.2.1項を参照).

7 SPIバス

7.1 概要

SPIはもともとモトローラのデバイスで使われたバスのひとつです.VS1011eのシリアル・データ・インターフェースSDI(7.3項,8.4項),およびシリアル・コントロール・インターフェースSCI(7.5項,8.5項)の両方に,このバスが採用されています.

7.2 SPIバスの端子説明

7.2.1 VS1002ネイティブ・モード(Newモード)

SM_SDINEWを"1"にセットするとこのモードが有効になります.この時,DCLK,SDATA,BSYNC端子は,それぞれGPIO2,GPIO3,XDCS端子として機能が置き換えられます.

|

SDI端子

|

SCI端子

|

説明

|

|

XDCS

|

XCS

|

アクティブ"L"のチップ・セレクト入力です.この端子を"H"にするとシリアル・インターフェースは強制的にスタンバイ・モードになり,その時点でのオペレーションは終了されます.さらにシリアル出力(SO端子)は強制的にハイ・インピーダンス状態になります.もしSM_SDISHAREが"1"の場合にはXDCSは使われません.代わりにそれに相当する信号が,XCSの反転により内部的に生成されます.

|

|

SCK

|

シリアル・クロック入力です.このクロックは内部でレジスタ・インターフェースのマスタ・クロックとしても使われます.

SCKは断続的,連続的のどちらも可能です.いずれの場合でも,XCSが"L"になった後の最初の立上りエッジが1番目のビットの取り込みタイミングとなります.

|

|

SI

|

シリアル入力です.チップ・セレクトが有効ならば,SCKの立上りエッジにてSIがサンプルされます.

|

|

−

|

SO

|

シリアル出力です.リード動作時,SCKの立下りエッジにてデータがシフト出力されます.

ライト動作においてSOはハイ・インピーダンス状態を保持します.

|

7.2.2 VS1001互換モード

SM_SDINEWが"0"のとき,このモードになります(デフォルト).このモードでは,DCLK,SDATA,BSYNC端子の機能がそのまま有効になります.

|

SDI端子

|

SCI端子

|

説明

|

|

−

|

XCS

|

アクティブ"L"のチップ・セレクト入力です.この端子を"H"にするとシリアル・インターフェースは強制的にスタンバイ・モードになり,その時点でのオペレーションは終了されます.さらにシリアル出力(SO端子)は強制的にハイ・インピーダンス状態になります.SDI用のチップ・セレクトはありません.SDIは常に有効です.

|

|

BSYNC

|

−

|

SDIデータはBSYNCの立上りエッジをもって同期が取られます.

|

|

DCLK

|

SCK

|

シリアル・クロック入力です.このクロックは内部でレジスタ・インターフェースのマスタ・クロックとしても使われます.

SCKは断続的,連続的のどちらも可能です.いずれの場合でも,XCSが"L"になった後の最初の立上りエッジが1番目のビットの取り込みタイミングとなります.

|

|

SDATA

|

SI

|

シリアル入力です.XCSが"L"ならば,SCKの立上りエッジにてSIがサンプルされます.

|

|

−

|

SO

|

シリアル出力です.リード動作時,SCKの立下りエッジにてデータがシフト出力されます.

ライト動作においてSOはハイ・インピーダンス状態を保持します.

|

7.3 シリアル・データ・インターフェース(SDI)の通信プロトコル

7.3.1 概要

シリアル・データ・インターフェースはスレーブ・モードで動作します.したがってDCLK信号は外部から供給する必要があります.データ(SDATA信号)を取り込むタイミングは設定によりDCLKの立上り,立下りのどちらでも可能です(8.6項を参照).

VS1011eへのデータ入力には"バイト同期"が必要です.各バイト内のビット順は,SCI_MODEの設定(8.6項)によりMSbファーストかLSbファーストを選択できます.

(訳注:"バイト同期"とは,データの送り手と受け手の両者間でビット列のバイト境界を一致させることを意味します)

7.3.2 VS1002ネイティブ・モード(Newモード)時のSDI

VS1002ネイティブ・モード(VS1011eでも利用可能)では,XDCS(SM_SDISHAREが"1"のときはXCS)信号によりバイト同期が行われます.

バイトの転送途中でXDCS(またはXCS)の状態を変化させてはいけません.例えばデータブロックの送出ごと,または数Kバイトの送出ごとにXDCS(またはXCS)のレベルを遷移させ,ホストとVS1011eの同期を確実なものにしてください.これは,仮にVS1011eが実装された基板上でグリッチなどが発生したとしても,常にデータ同期を維持するために必要です.

新規の設計ではVS1002ネイティブモードの採用が推奨されます.この方が後述のBSYNC信号を生成する方法よりも容易に実現できます.

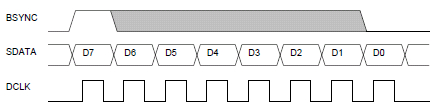

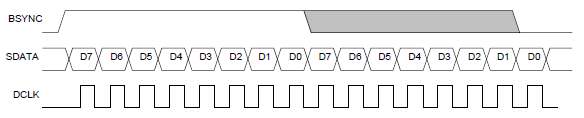

7.3.3 VS1001互換モード時のSDI

|

図5 BSYNC信号 - 1バイト転送時

|

VS1001互換モードの場合には,入力されるビット・ストリームのバイト境界に正しく位置合わせされたBSYNC信号を生成する必要があります.BSYNC信号が"H"となった最初のサンプリング・エッジ(極性設定により立上りまたは立下り)でのデータが,バイトの最初のビットとみなされます.このビットはLSbファースト設定の場合はLSbとして,MSbファースト設定の場合はMSbとして扱われます.そしてバイトの最終ビットを受信したとき,BSYNCが"H"のままであった場合には,続く8ビットも有効なデータとして引き続き取り込まれます.

|

図6 BSYNC信号 - 2バイト転送時

|

新規設計でVS1001互換モードを採用することは推奨されません.

7.4 データ・リクエスト端子DREQ

DREQ端子/信号は,VS1011eの内蔵FIFOがデータ受信可能であることを示します.DREQが"H"ならば,最低32バイトのSDIデータまたはSCIコマンド1個の入力が可能です.この条件が満たされない時,DREQは"L"になります.この時送り手は新たなデータ転送を開始してはいけません.

32バイトの安全領域があるため,32バイトまでならDREQの状態をチェックすることなく連続して送ることが出来ます.これは低速なマイクロコントローラによるVS1011eの制御をより容易にします.

注意:DREQはバイトの転送途中などを含め不特定のタイミングでレベルが変化します.したがってDREQは,次のバイト・データを送出できるかどうかを決めるためだけに使用してください.すでに開始したバイト転送を中断してはいけません.

注意:VS1002以前のVS10XX製品において,DREQはSDI専用でした.VS1011eでは,DREQはSCIのステータス表示としても使用されます.

7.5 シリアル・コマンド・インターフェース(SCI)の通信プロトコル

7.5.1 概要

シリアル・コマンド・インターフェースSCI(8.5項)のプロトコルは,常にインストラクション・バイトとアドレス・バイト,そして16ビットのデータ・ワードで構成されます.リード,ライトの各オペレーションにより,各レジスタの内容を読み,書きできます.データ・ビットは常にクロックの立上りエッジでサンプルされます.したがってデータの更新はクロックの立下りで行うようにして下さい.各バイトは常にMSbファーストで送受信されます.

オペレーションは8ビットのインストラクション・バイト(オペコード)の値により規定されます.サポートされているインストラクションはレジスタのリードとライトです.次の表を参照してください.

|

インストラクション

|

|

名前

|

オペコード

|

オペレーション

|

|

READ

|

0000 0011

|

リード・データ

|

|

WRITE

|

0000 0010

|

ライト・データ

|

注意:VS1011eは各SCIオペレーションの転送直後,DREQに"L"を出力します."L"の継続時間はオペレーションによって異なります.DREQが"L"の間は,次のSCI/SDIオペレーションを開始してはいけません.

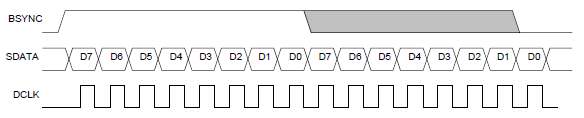

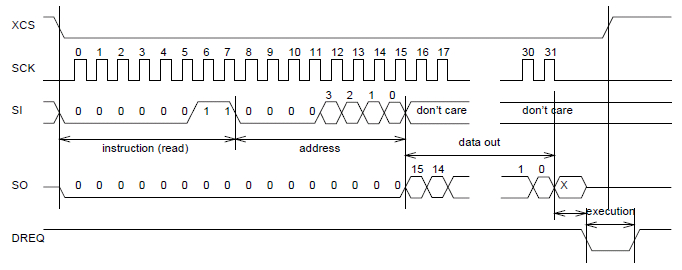

7.5.2 SCIリード

|

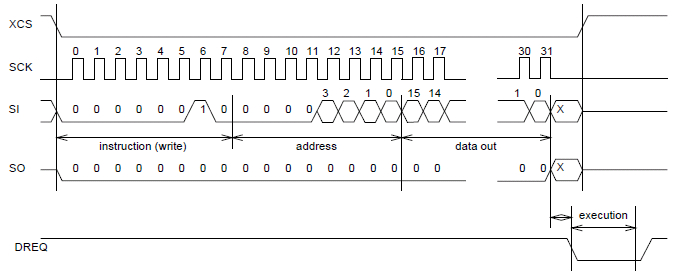

図7 SCIワード・リード

|

VS1011eの内部レジスタは次の手順で読み出せます(図7).まず,XCSを"L"にしてデバイス・セレクトを有効にします.次に,リード・オペコード(0x3),8ビットのレジスタ・アドレス,2バイトのダミー・データを順次SIへ送信します.ダミー・データの値は何でもかまいません.図7のとおり,このダミー・データの送出と並行して,送られたアドレスに対応するレジスタの内容16ビットが,SO端子からシフト出力されます.

シフト出力の完了後はXCSを"H"に戻して下さい.

このリード・オペレーションの内部処理時に,わずかの期間DREQが"L"になります.これは非常に短期間なので,特に配慮は必要ありません.

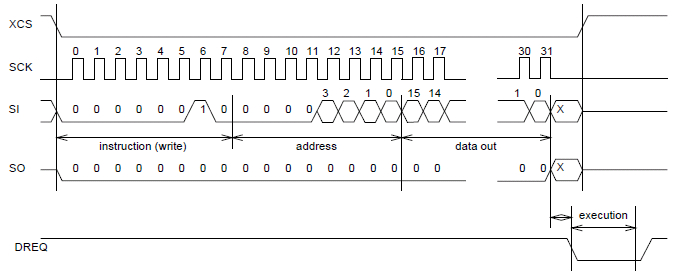

7.5.3 SCIライト

|

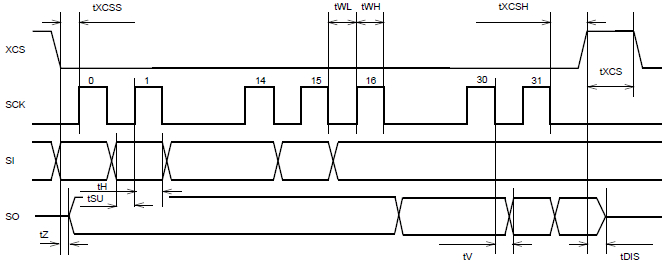

図8 SCIワード・ライト

|

VS1011eの内部レジスタへは次の手順でライトできます(図8).まず,XCSを"L"にしてデバイス・セレクトを有効にします.次に,ライト・オペコード(0x2),8ビットのレジスタ・アドレス,2バイトのライト・データを順次SIへ送信します.

最終クロックが送られた後に,ライト・シーケンスを終了させるためXCSを"H"にして下さい.

最終ビットが送られた後,DREQが"L"に駆動され,内部処理が実行中であることを示します(図8の"execution").この実行時間はレジスタとその値によって変動します(詳細は8.6項を参照).もしもその最大時間よりも,マイクロコントローラによる次のSCIコマンドまたはSDIバイト送出のほうが速い場合,DREQが"H"に戻るよりも前にそのSCI/SDIオペレーションを完了させてはいけません.

(訳注:この説明は7.5.1項の最後の記述と矛盾します.図10と図12のタイミング規定と併せると,ここでの説明の方が正しいと思われます.しかしもし期待通りの動作が得られないときには,DREQ="L"とSCI転送がオーバラップしないようにしてみてください.)

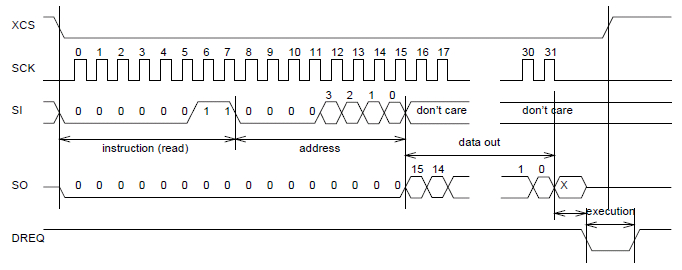

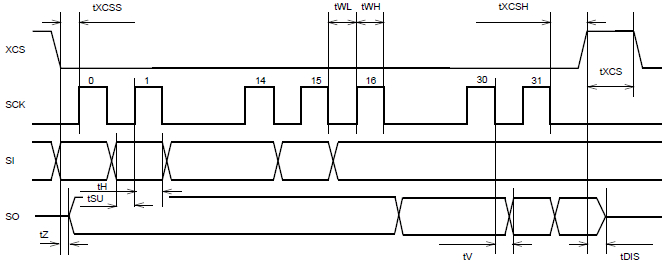

7.6 SPIタイミング・ダイアグラム

|

図9 SPIタイミング・ダイアグラム

|

|

記号

|

Min

|

Max

|

単位

|

|

tXCSS

|

5

|

|

ns

|

|

tSU

|

-26

|

|

ns

|

|

tH

|

2

|

|

XTALI周期

|

|

tZ

|

0

|

|

ns

|

|

tWL

|

2

|

|

XTALI周期

|

|

tWH

|

2

|

|

XTALI周期

|

|

tV

|

|

2+(25ns[1])

|

XTALI周期

|

|

tXCSH

|

-26

|

|

ns

|

|

tXCS

|

2

|

|

XTALI周期

|

|

tDIS

|

|

10

|

ns

|

[1] 25nsは負荷容量が100pFの場合です.容量が少ない場合,この時間は短くなります.

注意:tHに加えてtWL,tWHに最小2クロック周期が必要なため,リード・オペレーションでの最高速はVS1011eの外部クロックXTALIの1/6になります.ライト・オペレーションの最高速はXTALIの1/4です.(訳注:ここでのtHはtVの誤りと思われます)

注意:負数は信号同士の変化する順番が図の規定と逆になることを表します.

7.7 SM_SDINEWおよびSM_SDISHARED有効時のSPI動作例

7.7.1 2回のSCIライト

|

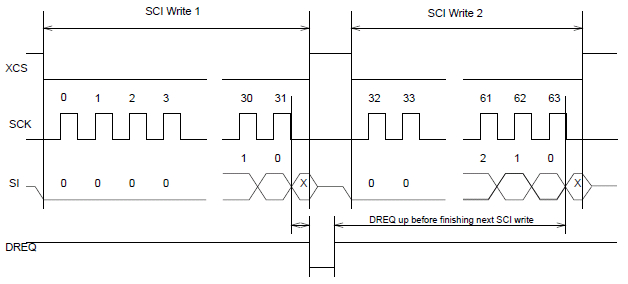

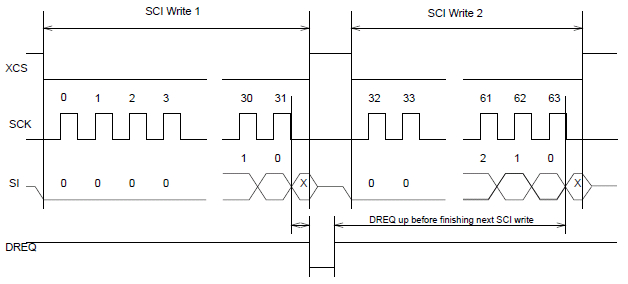

図10 2回のSCIオペレーション

|

図10は連続する2回のSCIオペレーションを示しています.各オペレーションごとにxCSを"H"にして,インアクティブ状態を作る必要があることに注意してください.併せてDREQも図の要件を満たす必要があります.

7.7.2 2回のSDIバイト転送

|

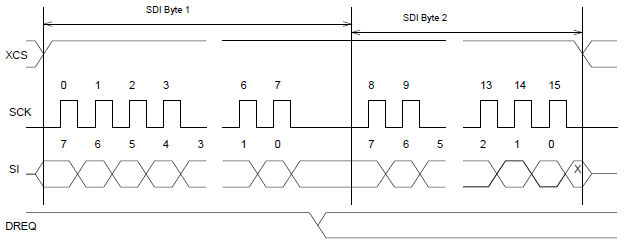

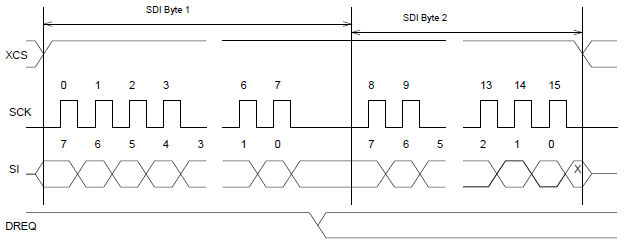

図11 2回のSDIバイト転送

|

図11のとおり,SDIデータはxCSの立上りエッジをもって同期が取られます.しかし個々のバイトごとに同期を取る必要はありません.

7.7.3 SCIオペレーションをはさんだ2回のSDIバイト転送

|

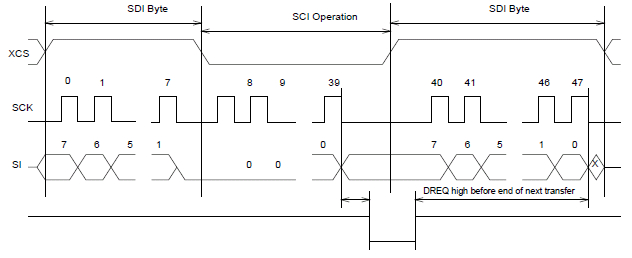

図12 SCIオペレーションをはさんだ2回のSDIバイト転送

|

図12はSDIオペレーション間にSCIオペレーションを差し挟む場合を示しています.xCSエッジはSDIおよびSCIの両方に対して同期を取るために使用されます.DREQについても図の要件を満たすようにしてください.

8 機能解説

8.1 主な機能

VS1011eの基盤は独自のディジタル・シグナル・プロセッサVS_DSPです.加えて,MPEG,WAV PCM,WAV IMA ADPCMオーディオのデコードに必要なプログラムおよびデータ・メモリ,シリアル・インターフェース,マルチ・レートのステレオ・オーディオDAC,アナログ出力アンプとフィルタを全て内蔵しています.

VS1011eはMPEG1.0,2.0のレイヤI,II,III,さらにMPEG2.5レイヤIIIについて,レイヤIIIの可変ビット・レート(VBR)を含む全てのビットレート,サンプルレートを再生できます.ただしレイヤIおよびIIをデコードするには,別途その機能を有効化する必要があります.

8.2 サポートされるオーディオ・コーデック

|

凡例

|

|

記号

|

説明

|

|

+

|

サポートされるフォーマット

|

|

-

|

存在するがサポートされないフォーマット

|

|

?

|

テストされていないフォーマット

|

| |

存在しないフォーマット

|

8.2.1 サポートされるMP1(MPEG レイヤI)フォーマット

MPEG 1.0:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

32

|

64

|

96

|

128

|

160

|

192

|

224

|

256

|

288

|

320

|

352

|

384

|

416

|

448

|

|

48000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

44100

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

32000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

MPEG 2.0:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

32

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

144

|

160

|

176

|

192

|

224

|

256

|

|

24000

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

|

22050

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

|

16000

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

?

|

8.2.2 サポートされるMP2(MPEG レイヤII)フォーマット

MPEG 1.0:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

32

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

160

|

192

|

224

|

256

|

320

|

384

|

|

48000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

44100

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

32000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

MPEG 2.0:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

8

|

16

|

24

|

32

|

40

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

144

|

160

|

|

24000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

22050

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

16000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

8.2.3 サポートされるMP3(MPEG レイヤIII)フォーマット

MPEG 1.0[1]:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

32

|

40

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

160

|

192

|

224

|

256

|

320

|

|

48000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

44100

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

32000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

MPEG 2.0[1]:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

8

|

16

|

24

|

32

|

40

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

144

|

160

|

|

24000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

22050

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

16000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

MPEG 2.5[1]:

|

サンプルレート/Hz

|

ビットレート/kbit/s

|

|

|

8

|

16

|

24

|

32

|

40

|

48

|

56

|

64

|

80

|

96

|

112

|

128

|

144

|

160

|

|

12000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

11025

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

|

8000

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

+

|

[1] 併せて可変ビットレート(VBR)もサポートされます.

注意:全てのビットレートおよびサンプル・レートに対して低音強調と高音制御を加えたデコードを行うためには,最低でも24.0MHzの内部クロック(24.0MHzの外部供給クロック,または12.0MHzの外部供給クロックとクロック・ダブラの組み合わせ)が必要です.

8.2.4 サポートされるRIFF WAVフォーマット

最も一般的なRIFF WAVサブフォーマットがサポートされています.

|

フォーマット

|

名称

|

サポート状態

|

備考

|

|

0x01

|

PCM

|

+

|

16ビットおよび8ビット,48KHz以下任意のサンプルレート

|

|

0x02

|

ADPCM

|

-

|

|

|

0x03

|

IEEE_FLOAT

|

-

|

|

|

0x06

|

ALAW

|

-

|

|

|

0x07

|

MULAW

|

-

|

|

|

0x10

|

OKI_ADPCM

|

-

|

|

|

0x11

|

IMA_ADPCM

|

+

|

48KHz以下任意のサンプルレート

|

|

0x15

|

DIGISTD

|

-

|

|

|

0x16

|

DIGIFIX

|

-

|

|

|

0x30

|

DOLBY_AC2

|

-

|

|

|

0x31

|

GSM610

|

-

|

|

|

0x3b

|

ROCKWELL_ADPCM

|

-

|

|

|

0x3c

|

ROCKWELL_DIGITALK

|

-

|

|

|

0x40

|

G721_ADPCM

|

-

|

|

|

0x41

|

G728_CELP

|

-

|

|

|

0x50

|

MPEG

|

-

|

|

|

0x55

|

MPEGLAYER3

|

+

|

MP3モードのサポート用.8.2.3項参照

|

|

0x64

|

G726_ADPCM

|

-

|

|

|

0x65

|

G722_ADPCM

|

-

|

|

8.3 VS1011eのデータ・フロー

|

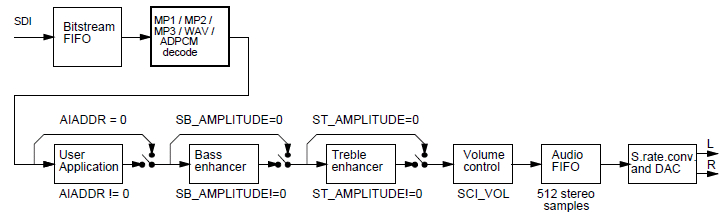

図13 VS1011eのデータ・フロー

|

まず,SDIバスからMPEGまたはWAVのオーディオ・データが入力され,デコードされます.

デコード後,SCI_AIADDRが"0"でない場合は,そのレジスタが指すアドレスからアプリケーション・コードが実行されます.詳細はVS10XXアプリケーション・ノート"User

Applications"を参照してください.

次にデータは,SCI_BASSの設定に基づいて,低音および高音強調ユニットへと送られ,さらにボリューム・コントロール・ユニットを経て,データはオーディオFIFOへ格納されます.

オーディオFIFOに格納されたデータは,オーディオ割り込み(10.9.1項参照)により読み出され,サンプル・レート・コンバータおよびDACへと送られます.オーディオFIFOのサイズはステレオ(2×16ビット)で512サンプル分,もしくは2KiBです.

サンプル・レート・コンバータは各種サンプル・レート信号をCLKI/512へと変換し,DACへ送ります.DACでステレオのアナログ信号に変換された信号は,最後にヘッドフォン・アンプで増幅されます.

8.4 シリアル・データ・インターフェース(SDI)

シリアル・データ・インターフェースは,MP3データおよびWAVデータを転送するためのインターフェースです.

併せて,9章で説明する各種テストの実行時にも使用されます.

8.5 シリアル・コントロール・インターフェース(SCI)

シリアル・コントロール・インターフェースはSPIバス規格と互換性があります.転送されるデータは常に16ビットです.VS1011eは,このインターフェースを通した各種レジスタへのリード,ライトによって制御されます.

このコントロール・インターフェースにより,主に次の要素が制御されます.

・オペレーション・モードやクロック,組み込みエフェクト類の制御.

・ステータス情報,ヘッダ情報へのアクセス.

・エンコード・データへのアクセス.

・ユーザ・プログラムのアップロード.

・入力データの供給.

8.6 SCIレジスタ

|

SCIレジスタ(先頭には"SCI_"が付く)

|

|

アドレス

|

種類

|

初期値

|

時間[1]

|

省略名

|

説明

|

|

0x0

|

rw

|

0

|

70CLKI[4]

|

MODE

|

モード・コントロール

|

|

0x1

|

rw

|

0x2C[3]

|

40CLKI

|

STATUS

|

VS1011eのステータス

|

|

0x2

|

rw

|

0

|

2100CLKI

|

BASS

|

内蔵の低音/高音強調

|

|

0x3

|

rw

|

0

|

80XTALI

|

CLOCKF

|

クロック周波数+逓倍器

|

|

0x4

|

rw

|

0

|

40CLKI

|

DECODE_TIME

|

再生時間[秒]

|

|

0x5

|

rw

|

0

|

3200CLKI

|

AUDATA

|

各種オーディオ・データ

|

|

0x6

|

rw

|

0

|

80CLKI

|

WRAM

|

RAMリード/ライト

|

|

0x7

|

rw

|

0

|

80CLKI

|

WRAMADDR

|

RAMリード/ライトのベース・アドレス

|

|

0x8

|

r

|

0

|

-

|

HDAT0

|

ストリーム・ヘッダ・データ0

|

|

0x9

|

r

|

0

|

-

|

HDAT1

|

ストリーム・ヘッダ・データ1

|

|

0xA

|

rw

|

0

|

3200CLKI[2]

|

AIADDR

|

アプリケーションの開始アドレス

|

|

0xB

|

rw

|

0

|

2100CLKI

|

VOL

|

ボリューム制御

|

|

0xC

|

rw

|

0

|

50CLKI[2]

|

AICTRL0

|

アプリケーション・コントロール・レジスタ0

|

|

0xD

|

rw

|

0

|

50CLKI[2]

|

AICTRL1

|

アプリケーション・コントロール・レジスタ1

|

|

0xE

|

rw

|

0

|

50CLKI[2]

|

AICTRL2

|

アプリケーション・コントロール・レジスタ2

|

|

0xF

|

rw

|

0

|

50CLKI[2]

|

AICTRL3

|

アプリケーション・コントロール・レジスタ3

|

[1] これはレジスタに値を設定した後,DREQが"L"を保持する時間(実行時間)の最大値です.実行時間100クロック・サイクル未満のレジスタ・ライトについては,DREQのチェックを省略してもかまいません.

[2] さらにユーザ・アプリケーションの実行時間を加える必要があります.

[3] この値はファームウェアにより直ちに0x28に更新されます.その後100ms以内にさらに0x20へと更新されます.

(訳注:ここでの"ファームウェア"とはVS1011eに元々組み込まれている内蔵プログラムのことです.したがってユーザから見ると,この値はリセット時は0x2Cで,その直後に0x28に変化し,さらに100ms以内に"自動的に"0x20になります.詳しくは8.6.2項を参照)

[4] ソフトウェア・リセットの場合に限り最大9600XTALIとなります.

もしSCIライトが完了したときDREQが"L"ならば,DREQはそのライト後そのまま"L"を保持することに注意してください.

8.6.1 SCI_MODE(RW)

SCI_MODEはVS1011eの動作を制御するために使われます.

|

ビット

|

名称

|

機能

|

値

|

説明

|

|

0

|

SM_DIFF

|

差動

|

0

1

|

通常の同相オーディオ

左チャンネルを反転

|

|

1

|

SM_LAYER12

|

MPEGレイヤI,II許可

|

0

1

|

禁止

許可

|

|

2

|

SM_RESET

|

ソフト・リセット

|

0

1

|

リセットしない

リセットする

|

|

3

|

SM_OUTOFWAV

|

WAVデコードの中断

|

0

1

|

禁止

許可

|

|

4

|

SM_SETTOZERO1

|

常に0

|

0

1

|

正常

設定禁止

|

|

5

|

SM_TESTS

|

SDIテスト許可

|

0

1

|

動作禁止

動作許可

|

|

6

|

SM_STREAM

|

ストリーム・モード

|

0

1

|

禁止

許可

|

|

7

|

SM_SETTOZERO2

|

常に0

|

0

1

|

正常

設定禁止

|

|

8

|

SM_DACT

|

DCLKアクティブ・エッジ

|

0

1

|

立上り

立下り

|

|

9

|

SM_SDIORD

|

SDIビット順

|

0

1

|

MSbファースト

LSbファースト

|

|

10

|

SM_SDISHARE

|

SPIチップ・セレクトの共用

|

0

1

|

禁止

許可

|

|

11

|

SM_SDINEW

|

VS1002ネイティブ・モード

|

0

1

|

禁止

許可

|

|

12

|

SM_SETTOZERO3

|

常に0

|

0

1

|

正常

設定禁止

|

|

13

|

SM_SETTOZERO4

|

常に0

|

0

1

|

正常

設定禁止

|

SM_DIFFをセットすると左チャンネル出力が反転されます.ステレオ入力の場合,仮想的なサラウンド効果が得られます.モノラル入力の場合には,左右両チャンネル出力を使った差動出力が簡単に得られます.

SM_LAYER12は,MPEG1と2のレイヤIIIに加えて,レイヤI,IIのデコード機能を有効にするかどうかを設定します.注意:もしレイヤIおよびレイヤIIのデコード機能を有効にする場合には,それらのフォーマットを使用することにより生じうる全ての特許問題について責任を負う必要があります.MPEG1.0/2.0レイヤIIIのジョイント・ライセンスの範囲は,レイヤIおよびIIに係る特許の全てを網羅していません.

SM_RESETに"1"をセットすると,デバイスはソフトウェア的にリセットされます.このビットは自動的にクリアされます.

SM_OUTOFWAVをセットすると,WAVファイルのデコード中に再生を中断できます.その後SM_OUTOFWAVが"0"になるまで,SDIに0を送ってください.もし,このSM_OUTOFWAVのチェックを省略したいときは,128個の0を送出してください.

SM_TESTSをセットするとSDIテスト機能が有効になります.詳しくは9.7項を参照してください.

SM_STREAMはVS1011eのストリーム・モードを有効にします.このモードにおいては,データをできるだけ一定の間隔(かつ512バイト未満のデータブロックごとが適当)で送出してください.VS1011eは再生速度を5%以内で変動させ,内部バッファの使用量が1/2を維持するように調整します.最高の音質を得るためには,平均転送速度の誤差を0.5%以内に抑えてください.またビットレートは160kbit/sを超えないようにするとともに,VBRは使わないでください.詳細はVS10XXアプリケーションノート"Streaming"を参照してください.

SM_DACTはSDIにおけるデータ・クロックのアクティブ・エッジを定義します.もし"0"ならデータは立上りエッジでサンプルされ,"1"なら立下りエッジでサンプルされます.

SM_SDIORDが"0"のとき,SDI上のデータはMSbファーストとみなされます.SM_SDIORDを"1"にすることにより,SDIデータのビットの並びを逆,すなわちビット0が最初に送られ,ビット7が最後となる順番にすることができます.ただしバイトの並びは変わりません.またこの設定はSCIバスに影響を与えません.

SM_SDISHAREをセットすることにより,SCIとSDIでひとつのチップ・セレクト信号を共有できます.説明は7.2項を参照してください.この機能を使う場合には併せてSM_SDINEWがセットされている必要があります.

SM_SDINEWをセットするとVS1002ネイティブ・モードが有効になります.7.2.1項および7.3.2項を参照してください.

8.6.2 SCI_STATUS(RW)

SCI_STATUSはVS1011eの現在の状態を示すとともに,グリッチ音が生じないシャットダウン手段をユーザに提供します.

|

名称

|

ビット

|

説明

|

|

SS_VER

|

6:4

|

バージョン情報

|

|

SS_APDOWN2

|

3

|

アナログ・ドライバ・パワーダウン

|

|

SS_APDOWN1

|

2

|

アナログ・インターナル・パワーダウン

|

|

SS_AVOL

|

1:0

|

アナログ・ボリューム・コントロール

|

SS_VERは,VS1001では0,VS1011では1,VS1002およびVS1011eでは2,VS1003では3がそれぞれ設定されます.併せてSCI_MODEの値によりVS1002とVS1011eの識別ができます.リセット後,VS1011eではSM_SDINEW=0,VS1002ではSM_SDINEW=1が設定されます.

SS_APDOWN2はアナログ・ドライバ・パワーダウンを制御します.通常このビットは内蔵のシステム・ファームウェアによって制御されます.しかし,パワー・オフ時の過渡状態を最小限に抑えたい場合には,まずこのビットをセットし,さらに最低数msec待ってからデバイスをリセットします.

SS_APDOWN1は内部アナログ回路のパワーダウンを制御します.このビットはシステム・ファームウェアが使用します(ユーザは使えません).

SS_AVOLはアナログ・ボリュームを制御します.0=-0dB,1=-6dB,3=-12dBです.このビットはシステム・ファームウェアが使用します(ユーザは使えません).

8.6.3 SCI_BASS(RW)

|

名称

|

ビット

|

説明

|

|

ST_AMPLITUDE

|

15:12

|

高音制御,1.5dB刻み(-8〜7,0=off)

|

|

ST_FREQLIMIT

|

11:8

|

下限周波数,1000Hz刻み(0〜15)

|

|

SB_AMPLITUDE

|

7:4

|

低音強調,1dB刻み(0〜15,0=off)

|

|

SB_FREQLIMIT

|

3:0

|

下限周波数,10Hz刻み(2〜15)

|

低音強調VSBEは,クリッピングを生じさせることなくヘッドフォンを最大限に生かす強力な低音域増強DSPアルゴリズムです.

VSBEはSB_AMPLITUDEに0以外の値をセットすると有効になります.SB_AMPLITUDEの値は好みにより調整してください.またSB_FREQLIMITは,ユーザのオーディオ・システムが再生できる最低周波数の約1.5倍位を目安に設定してください.例えば,SCI_BASSに0x00f6を設定すると,60Hz以下において15dB強調されます.

注意:VSBEはクリッピングの発生を抑えようとするので,最大音量に対して余裕を持ったボリューム設定でないと,ダイナミックな音源の低音を十分に強調することはできません.また音源そのものに強調すべき低音成分が含まれている必要があります.

高音制御VSTCはST_AMPLITUDEに0以外の値をセットすると有効になります.例えばSCI_BASSに0x7a00をセットすると,10KHzより上が10.5dB強調されます.

サンプルレート44100Hzにおいて,低音強調は約2.1MIPS,高音制御は約1.2MIPSを使用します.両者は同時に使用できます.

8.6.4 SCI_CLOCKF(RW)

SCI_CLOCKFは,クロック入力XTALIが24.576MHzでない場合の周波数を設定するレジスタです.XTALIは2KHz刻みで設定できます.つまり,このレジスタへの設定値は式 XTALI/2000 (XTALIの単位はHz)でもとめた値です.ハードウェア的に動作可能な上限値はありますが,設定できる値の範囲は0〜32767です.

一方24.576MHzよりも低速なクロックの場合,全てのサンプル・レートに対応することはできなくなります.例えば24MHzの場合なら,サンプル・レート48kHzのデータの再生音は2.5%音程がずれてしまいます.

SCI_CLOCKFのMSBに"1"をセットすると,次回サンプル・レートが設定された際に内蔵のクロック・ダブラが有効になります.

注意:SCI_CLOCKFはオーディオ・データのデコード開始に先立って設定されなければなりません.そうでない場合,サンプル・レートが正しく設定されません.

例1:クロックが26MHzの場合,レジスタ設定値は26000000/2000=13000です.

例2:13MHzの外部クロックと内蔵クロック・ダブラを組み合わせて内部クロック26MHzを得る場合,レジスタ設定値は0x8000+13000000/2000=39268となります.

例3:24.576MHzを使用する場合,レジスタ設定値は24576000/2000=12288か,またはデフォルト値の0とすることができます.したがってこの周波数の場合,SCI_CLOCKFは設定する必要はありません.

8.6.5 SCI_DECODE_TIME(RW)

正常なデータをデコードしている時,その時点までのデコード時間を秒単位で表した値がこのレジスタに入ります.

ユーザによりこの値を書き換えることは可能です.しかしその場合,新しい値により2度書き込みを行う必要があります.

SCI_DECODE_TIMEの値はソフトウェア・リセットごとに初期化されます.

8.6.6 SCI_AUDATA(RW)

正常なデータをデコードしている時,このレジスタSCI_AUDATAのビット15:1とビット0のそれぞれに,現在のサンプル・レートおよびチャンネル数が入ります.ビット15:1にはサンプル・レートの1/2の値が入り,ビット0はモノラルなら0,ステレオなら1が入ります.このレジスタを書き換えると,実行中であってもサンプル・レートが変更されます.

例:44100Hzステレオの場合,読み出される値は0xAC45(44101).

例:11025Hzモノラルの場合,読み出される値は0x2B10(11024).

例:0xAC80を書き込むと,サンプル・レートは44160Hzに変更されます.しかしステレオ・モードは変更されません.

8.6.7 SCI_WRAM(RW)

SCI_WRAMは,アプリケーションプログラムとデータを,それぞれインストラクションRAMおよびデータRAMにアップロードするために使われます.SCI_WRAMによるリード/ライトに先立って,まずSCI_WRAMADDRで開始アドレスを初期化しておく必要があります.なおSCI_WRAMのリード/ライト1回で転送できるのは16ビットであり,インストラクション・ワードは32ビットなので,インストラクション・ワードの場合には連続2回のリード/ライトが必要です.バイト順はビッグ・エンディアン(MSBが先)です.ワードのリード/ライトごとに内蔵のアドレスポインタが自動インクリメントされます.

8.6.8 SCI_WRAMADDR(RW)

SCI_WRAMADDRは,後に続くSCI_WRAMでリード/ライトされるメモリ・バスとプログラム・アドレスを設定します.

|

SM_WRAMADDR

先頭〜末尾

|

対象アドレス

先頭〜末尾

|

ビット/ワード

|

説明

|

|

0x1380〜0x13FF

|

0x1380〜0x13FF

|

16

|

XデータRAM

|

|

0x4780〜0x47FF

|

0x0780〜0x07FF

|

16

|

YデータRAM

|

|

0x8030〜0x84FF

|

0x0030〜0x04FF

|

32

|

インストラクションRAM

|

|

0xC000〜0xFFFF

|

0xC000〜0xFFFF

|

16

|

I/O

|

8.6.9 SCI_HDAT0およびSCI_HDAT1(R)

|

ビット

|

機能

|

値

|

説明

|

|

HDAT1[15:5]

|

syncword

|

2047

|

stream valid

|

|

HDAT1[4:3]

|

ID

|

3

|

ISO 11172-3 MPG 1.0

|

|

|

|

2

|

ISO 13818-3 MPG 2.0 (1/2-rate)

|

|

|

|

1

|

MPG 2.5 (1/4-rate)

|

|

|

|

0

|

MPG 2.5 (1/4-rate)

|

|

HDAT1[2:1]

|

layer

|

3

|

I

|

|

|

|

2

|

II

|

|

|

|

1

|

III

|

|

|

|

0

|

reserved

|

|

HDAT1[0]

|

protect bit

|

1

|

No CRC

|

|

|

|

0

|

CRC protected

|

|

HDAT0[15:12]

|

bitrate

|

|

see bitrate table

|

|

HDAT0[11:10]

|

sample rate

|

3

|

reserved

|

|

|

|

2

|

32/16/8KHz

|

|

|

|

1

|

48/24/12KHz

|

|

|

|

0

|

44/22/11KHz

|

|

HDAT0[9]

|

pad bit

|

1

|

additional slot

|

|

|

|

0

|

normal frame

|

|

HDAT0[8]

|

private bit

|

|

not defined

|

|

HDAT0[7:6]

|

mode

|

3

|

mono

|

|

|

|

2

|

dual channel

|

|

|

|

1

|

joint stereo

|

|

|

|

0

|

stereo

|

|

HDAT0[5:4]

|

extension

|

|

see ISO 11172-3

|

|

HDAT0[3]

|

copyright

|

1

|

copyrighted

|

|

|

|

0

|

free

|

|

HDAT0[2]

|

original

|

1

|

original

|

|

|

|

0

|

copy

|

|

HDAT0[1:0]

|

emphasis

|

3

|

CCITT J.17

|

|

|

|

2

|

reserved

|

|

|

|

1

|

50/15 microsec

|

|

|

|

0

|

none

|

SCI_HDAT0,SCI_HDAT1レジスタをリードすると,その時点でデコードされているMPEGストリームのヘッダ情報を得ることができます.VS1011eをリセットした直後は,この両レジスタの内容は0で初期化され,データが未検出であることを示します.

上表のSCI_HDAT0に含まれる"sample rate"フィールドの値は,次の表に従って解釈できます.

|

"sample rate"

|

ID=3/Hz

|

ID=2/Hz

|

ID=0,1/Hz

|

|

3

|

−

|

−

|

−

|

|

2

|

32000

|

16000

|

8000

|

|

1

|

48000

|

24000

|

12000

|

|

0

|

44100

|

22050

|

11025

|

またSCI_HDAT0に含まれる"bitrate"フィールドの値は,次の表にしたがって解釈できます.

|

"bitrate"

|

レイヤI [kbit/s]

|

レイヤII [kbit/s]

|

レイヤIII [kbit/s]

|

|

ID=3

|

ID=0,1,2

|

ID=3

|

ID=0,1,2

|

ID=3

|

ID=0,1,2

|

|

15

|

禁止

|

禁止

|

禁止

|

禁止

|

禁止

|

禁止

|

|

14

|

448

|

256

|

384

|

160

|

320

|

160

|

|

13

|

416

|

224

|

320

|

144

|

256

|

144

|

|

12

|

384

|

192

|

256

|

128

|

224

|

128

|

|

11

|

352

|

176

|

224

|

112

|

192

|

112

|

|

10

|

320

|

160

|

192

|

96

|

160

|

96

|

|

9

|

288

|

144

|

160

|

80

|

128

|

80

|

|

8

|

256

|

128

|

128

|

64

|

112

|

64

|

|

7

|

224

|

112

|

112

|

56

|

96

|

56

|

|

6

|

192

|

96

|

96

|

48

|

80

|

48

|

|

5

|

160

|

80

|

80

|

40

|

64

|

40

|

|

4

|

128

|

64

|

64

|

32

|

56

|

32

|

|

3

|

96

|

56

|

56

|

24

|

48

|

24

|

|

2

|

64

|

48

|

48

|

16

|

40

|

16

|

|

1

|

32

|

32

|

32

|

8

|

32

|

8

|

|

0

|

-

|

-

|

-

|

-

|

-

|

-

|

なおWAVファイルをデコードしている時は,SCI_HDAT0とSCI_HDAT1の値はそれぞれ0x7761と0x7665が読み出されます.

8.6.10 SCI_AIADDR(RW)

SCI_AIADDRは,SCI_WRAMADDRとSCI_WRAMレジスタにより前もって書き込まれたアプリケーション・コードの開始アドレスを示すレジスタです.アプリケーション・コードを使用しない場合には,このレジスタへの書き込みをしないままにするか,もしくは0で初期化します.詳細はVS10XXアプリケーション・ノート"User

Applications"を参照してください.

8.6.11 SCI_VOL(RW)

SCI_VOLはプレーヤのボリュームを制御します.左右各チャンネルに対して,それぞれ0〜254の範囲で値を設定でき,その値は最大音量からの減衰量を0.5dB刻みで表したものとなります.左チャンネルの設定値は上位バイト,右チャンネルは下位バイトに設定します.したがって最大音量ならば設定値は0x0000,最小音量(無音)ならば0xFEFEです.

例:左チャンネルのボリュームを-2.0dB,右チャンネルを-3.5dBに設定したい場合,レジスタへの設定値は(4×256)+7=0x407です.なお,起動時の設定はボリューム最大ですので注意してください.ソフトウェアをリセットしてもボリューム設定はリセットされません.

注意:SCI_VOLに0xFFFFを設定すると,アナログ・パワーダウン・モードが有効になります.

8.6.12 SCI_AICTRL[x](RW)

SCI_AICTRL[x]レジスタ(x=[0〜3])はユーザのアプリケーション・プログラムへアクセスする際に使用されます.

9 オペレーション

9.1 クロック

VS1011eは24.576MHzを標準とする単一のマスタ・クロックで動作します.外部回路からのクロック入力(XTALI端子に接続),もしくは内蔵の発振回路と外付けクリスタルの組み合わせ(XTALI,XTALO端子に接続)が可能です.内蔵のクロック・ダブラを併用することで,12.288MHz外部クロックから24.576MHzを得ることもできます.24.576MHzは,すべてのコーデックとサンプル・レート,ビットレートに対して高音および低音強調処理を加えても,高音質のオーディオ出力を得るために十分な周波数です.

9.2 ハードウェア・リセット

XRESET信号を"L"にするとVS1011eはリセットされ,すべてのコントロール・レジスタと内部状態が初期化されます.XRESET信号はいずれのクロックに対しても非同期です.またリセット・モードはフル・パワーダウン・モードとしても機能します.この時,VS1011eのディジタル部とアナログ部の両方とも最も低消費電力の状態になり,クロックは停止します.併せてXTALIとXTALO両端子はグランドに接地されます.

ハードウェア・リセット後,またはパワー・アップ時,ユーザはデコードを開始する前に,まずボリューム設定SCI_VOLやSCI_CLOCKF(入力クロック24.576MHzでない場合)などの基本的なレジスタを設定する必要があります.

9.3 ソフトウェア・リセット

時としてソフトウェア的なリセットが必要になることがあります.ソフトウェア・リセットは,SCI_MODEレジスタ(8.6.1項参照)のビット2をセットすると実行できます.セット後,2μs以上待ってから,DREQの状態をチェックしてください.DREQは少なくとも6000クロック・サイクルの間"L"を保持します.これは24.576MHzクロックの場合約250μsのディレイとなります.そしてDREQが"H"に立ち上がれば,通常の再生動作が可能となります.

もし低ビットレートのデータ・ストリームを使用していて,ソフトウェア・リセット時に音声出力の最後尾が途切れないようにしたい場合には,リセットをかける前に,そのデータ・ファイルの後に続けて2048個の0をSDIへ送信してください.

9.4 SPIブート

起動時にGPIO0端子が"1"にプルアップされている場合,VS1011eはSPI経由で外部メモリからのブートを試みます.

SPIブート時には,次の表のとおり,端子の機能が一部変更されます.

|

ノーマル・モード

|

SPIブート・モード

|

|

GPIO0

|

xCS

|

|

GPIO1

|

CLK

|

|

DREQ

|

MOSI

|

|

GPIO2

|

MISO

|

使用できる外部メモリはSPIバス型のシリアルEEPROMで,16ビット・アドレスを持つもの(すなわちメモリサイズは最低1KiB)です.シリアルの転送速度は24.576MHzクロックの場合で490KHzです.メモリの最初の3バイトは0x50,0x26,0x48でなければなりません.正しい記録フォーマットはVS10XXのアプリケーション・ノートを参照してください.

SPIブートが成功すると,SCI_MODEには0x0800がセットされています.

9.5 プレイ/デコード

これがVS1011eの通常の動作モードになります.SDIデータが順次デコードされます.デコードされたサンプル値は,内蔵のDACによりアナログ信号に変換されます.もしデコード可能なデータが見つからないときは,SCI_HDAT0とSCI_HDAT1には0がセットされ,アナログ出力はミュートされます.

またデコードすべきデータ入力がない場合は,VS1011eはアイドル・モード(デコード時よりも低消費電力の状態)へと移行し,有効なデータが入力されるのを待ちます.

9.6 PCMデータの入力

VS1011eへWAVファイル・ヘッダを送ることにより,PCMデコーダとしても使用することができます.ヘッダ中のlengthパラメータを0または0xFFFFFFFとしておくと,VS1011eはPCMモードを維持します.8ビット・リニアまたは16ビット・リニア・オーディオが,モノラル,ステレオともにサポートされます.

9.7 SDIテスト

VS1011eにはメモリ・テストやSCIバス・テスト,正弦波テストといったいくつかのテスト・モードが用意されています.

これらのテストはいずれも同様の手順で開始されます.それはまずハードウェア・リセットの後,SM_TESTSをセットし,SDIバスにテスト・コマンドを送信することです.テスト・コマンドは4バイトの特別なコマンド・シーケンスと,それに続く4バイトの0です.それぞれ以下で説明します.

(訳注:正弦波テストでの実験によれば,上記のハードウェア・リセットはソフトウェア・リセットでも代用できました)

9.7.1 正弦波テスト

正弦波テストは次の8バイトのシーケンスにより開始されます:0x53,0xEF,0x6E,n,0,0,0,0.

ここでnは正弦波を定義するための値で,次のように定められます.

|

nのビット

|

|

名称

|

ビット

|

説明

|

|

FsIdx

|

7:5

|

サンプル・レート・インデックス

|

|

S

|

4:0

|

正弦波スキップ・スピード

|

|

FsIdx

|

Fs

|

|

0

|

44100Hz

|

|

1

|

48000Hz

|

|

2

|

32000Hz

|

|

3

|

22050Hz

|

|

4

|

24000Hz

|

|

5

|

16000Hz

|

|

6

|

11025Hz

|

|

7

|

12000Hz

|

出力される正弦波の周波数Fは次式で求められます.

F=Fs×S/128.

例:n=126の場合.126=0b01111110なので,分割するとFsIdx=0b011=1(訳注:3の誤り)したがってFs=22050Hzです.一方S=0b11110=30なので,この結果正弦波の周波数Fは

F=22050Hz×30/128=5168Hz.

となります.

正弦波テストを終了するには,次のシーケンスを送信してください:0x45,0x78,0x69,0x74,0,0,0,0.

注意:正弦波テストの信号はディジタル・ボリューム・コントロールを通ります.したがって各チャンネルを個別にテストすることも可能です.

9.7.2 端子テスト

端子テストは次の8バイトのシーケンスで有効になります:0x50,0xED,0x6E,0x54,0,0,0,0.

このテストはチップ製造時の検査用です.

9.7.3 メモリ・テスト

メモリ・テスト・モードは次の8バイトのシーケンスにより開始されます:0x4D,0xEA,0x6D,0x54,0,0,0,0.

このシーケンスの後,200000クロック・サイクル待ってください.テスト結果はSCIレジスタのSCI_HDAT0を読み出すことで得られます.その値の中で"1"がセットされたビットの位置を次の表に当てはめて結果を解釈します.

|

ビット

|

マスク

|

意味

|

|

15

|

0x8000

|

テスト完了

|

|

14:7

|

|

未使用

|

|

6

|

0x0040

|

Mux test succeeded

|

|

5

|

0x0020

|

Good I RAM

|

|

4

|

0x0010

|

Good Y RAM

|

|

3

|

0x0008

|

Good X RAM

|

|

2

|

0x0004

|

Good I ROM

|

|

1

|

0x0002

|

Good Y ROM

|

|

0

|

0x0001

|

Good X ROM

|

|

|

0x807f

|

All ok

|

メモリ・テストはRAMの内容を書き換えますので注意してください.

9.7.4 SCIテスト

SCIテストは次の8バイトのシーケンスにより開始されます:0x53,0x70,0xEE,n,0,0,0,0.

ここでn-48がテスト対象のレジスタ番号になります.これにより指定されたレジスタの内容がSCI_HDAT0にコピーされます.対象としてHDAT0を指定すると,その内容はSCI_HDAT1へコピーされます.

例:nが48のとき,SCIレジスタ0(SCI_MODE)の内容が,SCI_HDAT0にコピーされます.

10 VS1011e内蔵レジスタ

10.1 本章を必要とするユーザ

ユーザが例えばDSPエフェクトのような独自の機能をVS1011eに追加したいと思うなら,そのためのソフトウェアが必要になります.しかし大部分のユーザにおいては,独自のプログラムを書くことや,またはこの章の内容について,心配する必要はありません.その中にはVLSI

Solutionのウェブ・サイトからソフトウェア・プラグインをダウンロードするだけの人も含まれます.

(以下この章は省略)

11 VS1011バージョン履歴

この章ではVS1011の世代間での相違点について説明します.

11.1 VS1011bとVS1011eの相違点,2005-07-13

・デコードの高速化:コーデック,ビットレート全種類に対して低音+高音制御を加えた処理をCLKI=24MHzで実行可能.

・SCI_BASSレジスタに高音制御を追加(8.6.3項).ラウドネス・プラグインは不要.

・IMA ADPCMをモノラル,ステレオともに再生可能(8.2.4項).

・SCI_WRAMを使ってレジスタ空間へのライトが可能(8.6.7項).

・SCI_WRAMを使ってメモリおよびレジスタ空間からのリードが可能(8.6.7項).

・MPEG1と2のレイヤI,IIについて選択的な再生を追加(8.2.2項,8.2.1項および8.6.1項).

・SPIブートを追加(9.4項).

・MPEG1,2,2.5のレイヤIIIのデコードがビットエラーに対してより強固に.

・MPEG2.5のデコードの互換性を向上.

・SCIオペレーション中,DREQは"L"(7.4項).

・メモリ・テスト中,DREQは"L"(7.4項).

・VS1011eでは,SCI_STATUSのSS_VERフィールド値は2.

11.2 VS1011bからVS1011eへ移行する場合の確認事項,2005-07-13

・SCI_STATUSのSS_VERフィールド値が2になりました.SCI_STATUSとSCI_MODEにより,VS1002とVS1011eは区別できます.つまりVS1011bはSS_VER=1でSM_SDINEW=0,VS1011eはSS_VER=2でSM_SDINEW=0,そしてVS1002はSS_VER=2でSM_SDINEW=1です.

・ラウドネス・プラグインに代えて,内蔵の低音強調と高音制御を使用してください.ラウドネス・プラグインも使用できますが,内蔵のものの方がより高速です.

12 本文書の改版履歴

この章では,この文書の重要な変更点について説明します.

12.1 VS1011e用バージョン1.04,2007-10-08

・VS1011eより、SOIC-28パッケージも鉛フリーRoHS対応を開始.

12.2 VS1011e用バージョン1.03,2005-09-05

・量産バージョン.暫定の記述を削除.

12.3 VS1011e用バージョン1.02,2005-07-13

・VS1011e用の新しい機能を追加(11.1項を参照).

12.4 VS1011b用バージョン1.01,2004-11-19

・存在しないSCIMB_POWERDOWNビットを削除.

・5.1.3項と5.2.2項にSOIC-28パッケージを追加.

12.5 VS1011b用バージョン1.00,2004-10-22

・4章の各表に正規の値を設定.

・5.2項において,DVDD2,DGND2,DGND3用にBGA-49のボールを再割り当て.

12.6 VS1011用バージョン0.71,2004-07-20

・未使用のGPIOに100KΩのプルダウンを追加する旨を5.2項に追記.

12.7 VS1011用バージョン0.70,2004-05-13

・SM_JUMPを削除.

12.8 VS1011用バージョン0.62,2004-03-24

・8.2項のサポートされるオーディオ・コーデックについて,より明確となるように記述を更新.

13 連絡先

VLSI Solution Oy

Hermiankatu 6-8 C

FIN-33720 Tampere

FINLAND

Fax: +358-3-316 5220

Phone: +358-3-316 5230

Email: sales@vlsi.fi

URL: http://www.vlsi.fi/

注意:ご質問があるときは,まずhttp://www.vlsi.fi/vs1011/faq/に目を通してください.

・・・本文ここまで.

誤訳など,お気づきの点がございましたらお知らせください.掲示板はこちらです.

なお,これはVS1011eを使う上で最低限必要な資料である「データシート」です.実際にプレーヤを作るにはさらに情報が必要かと思います.以下に,次のステップとなる情報源を挙げておきます.

★VS10XX APPL. NOTES

VS1011を含むVS10XXシリーズのアプリケーション・ノートです.こちらはプレーヤを作る上での方法や注意点などをより具体的に説明しています.例えば,以下はその第5章です.

5 音楽を再生するには (11,02)

この章ではVS1011/VS1002dの正しい起動法と音楽の再生法について説明します.

1.8章の説明にしたがってVS10xxに電源を入れます.

2.xRESETを"H"にします.

3.DREQが"H"になるまで待ちます.

4.SCI_MODEレジスタに,SM_SDINEWやSM_SDISHAREDを含め適切な値を設定します.

5.クロックが24.576MHzでない場合にはSCI_CLOCKFを設定します.

6.もしクロック・ダブラを使用し,かつSCI_CLOCKFへの設定を直ちに有効にしたい場合には,任意のサンプル・レートをSCI_AUDATAにライトして下さい.その10000クロック・サイクル後には,VS10xxの動作は倍速になっています.以後,より高速なSPIの転送速度が使用できます(12章参照).

7.ボリューム・レジスタSCI_VOLを設定します.

8.低音強調SCI_BASSを好みに応じて設定します.

9.もしVS10xxのRAMへロードするユーザ・プログラムがあるならば,SCI_WRAM,SCI_WRAMADDR,SCI_AIADDRを用いてダウンロードし,有効化して下さい.

10.DREQに関するルールを守りながら,VS10xxへのオーディオ・ファイルの転送を開始します.

11.曲データの転送終了後,未再生のオーディオ・データが残っていないことを確実にしたい場合には,さらに2048個の0をSDIへ転送して下さい.

12.もしユーザ・プログラムを有効にしているならば,AIADDRに0をライトして無効にします.

13.SCI_MODEレジスタのSM_RESETビットをセットします(ソフトウェア・リセット).

14.ステップ3へ戻ります.

その他アプリケーション・ノートはここにあります.

★VLSIModularPlayer Documentation

VLSI社純正の評価キット,"VS1011,VS1002 and VS1003 Decoder Evaluation Kit"用のファームウェアで,ソース・リストが公開されています.デバイス・メーカ自身によって作成された処理例ですので,とても参考になります.回路図なども公開されています.

△ページの先頭へ戻る

Copyright 2006-2008 Chiaki Nakajima.

All rights reserved.