|

SDカード・トランスポートを作ってみました −その2−

SDTrans192, SDTrans384

|

|

SDカード・トランスポートを

作ってみました

−その2−

SDTrans192

SDTrans384

2009年4月〜 進行中

|

2009年の春に作ったTimpy Rev7.0"改"により、SDカード・トランスポートの優位性を感じることができました。そこで、『この方式を突き詰めていくとどこまでいけるのだろう?』という興味のもと、手探りで始めたのがSDTrans192シリーズです。

》Rev1.0 : 動作確認のための試作

最初の目標は「192KHz、24ビットのWAVファイルを再生すること」でした。これが可能なのかどうかを確認するために、手配線で作った試作版です。

》Rev2.0 : 操作性の向上とプリント基板化

液晶パネルやボタンの追加など、操作性の改善を加えてプリント基板化した最初の版です。

2009年12月、ファームウェアとFPGAの改良により、192KHz以下なら32ビットまで、24ビットなら352.8KHzまで再生できるようになりました。

》Rev2.1 : 音質向上をねらってアートワーク変更

前作での経験を踏まえ、ディジタル信号のアナログ的振る舞いが音に与える影響を考慮して、基板設計を見直しました。

》Rev3.0 : 全面的な見直しと機能追加

Rev2.1で実証できた新しいアートワークの設計思想を全体に強く反映させました。回路面でもクロック・電源周りを中心に見直して、全面的に改良を加えました。新機能も追加されています。

★トランスポート本体としては、このSDTrans192 Rev3.0 (SDTrans384)が最新作です。

★最新版ファームウェアは3.22、FPGAが023です。

》Rev3.0+Syncオプション : DACをクロックマスタに

DACに供給されるマスタクロックの質は、音の良し悪しを左右する最重要項目です。でもそのクロックをトランスポートから供給するのは明らかに不自然です。

そこで、話題の高性能DACチップES9018を搭載したCapriceを改造して、超低ジッタのマスタクロック用オシレータ2個をDAC側に内蔵させました。従来とは逆に、SDTrans384がDACのマスタクロックを受けて同期動作する形です。さらにSDTrans384とDAC間を電気的に完全に絶縁しました。

後追いでDSD64、DSD128、DSD256にも対応しました。ファイルフォーマット(WAVまたはDFF)にしたがって、自動的に信号を切り替えて再生します。

》SDTrans-Sync-9018D : SDTrans-Sync方式デュアルモノDAC

Syncオプションと同じSDTrans-Sync方式を採りつつ、ES9018のデュアルモノ構成が楽しめるDAC基板を作ってみました。

》SDTrans-9018D-IV : SDTrans-Sync-9018D用 IV変換基板

SDTrans-Sync-9018Dの電流出力を電圧出力に変換するための基板です。

SDTrans192/SDTrans384には、DACその他のアナログ系は搭載されていません。ディジタル系だけです。それでも、ちょっとしたことで最終的な音質に大きな違いが現れます。その反面、かなりのことをしても大した影響がなかったりします。

『ディジタル処理のためのディジタル回路と、アナログ処理のためのディジタル回路は、アプローチが根本的に違う』ことを実感します。『ディジタル回路も詰まるところアナログ回路』とは昔から良く言われる言葉ですが、それに通じる部分なのでしょう。この辺の振る舞いがとても興味深く、底知れぬ奥深さを感じます。

|

》特徴(Rev3.0+Syncオプションにて)

★対応記録メディア : SDカード、SDHCカード

★対応ファイルシステム : FAT16、FAT32

★対応ファイル形式 :

(1)RIFF WAVファイル

・サンプルレート : 44.1KHz、48KHz、88.2KHz、96KHz、176.4KHz、192KHz、352.8KHz、384KHz

・ワードサイズ : 8ビット、16ビット、24ビット、32ビット

(2)DSDIFFファイル

・サンプルレート : 2.8MHz(DSD64)、5.6MHz(DSD128)、11.3MHz(DSD256)

・チャンネル数 : 2(ステレオ)

★出力信号形式 : I2S(C-MOS、LVDS出力)、DSD(C-MOS、LVDS出力)、S/PDIF(同軸)(注)

★マスタクロック

・使用デバイス : NDK製超低ジッタ型オシレータモジュール

・クロック周波数 : 98.3040MHz、90.3168MHz(自動切換)

・オシレータモジュールはDAC側に内蔵

★SDTrans384とDAC間は電気的に絶縁

★外部LSI制御用にI2Cインターフェースが利用可能

★SDカードに保存したオブジェクトファイルからファームウェアのアップデートが可能

★外部から動作の制御や状態のモニタができるリモートI/O端子

(注)352.8KHz、384KHzのWAVファイルおよびDSDファイルの場合、S/PDIF出力はできません。I2S、DSD出力のみとなります。

》Rev1.0 : 動作確認のための試作

SDTrans192の最初の目標は、「192KHz、24ビットのWAVファイルを再生すること」。これを実現するには、FATのクラスタチェーンをたどりながら、SDカードから平均転送レート9.216Mbps以上でWAVデータを読み出し、出力できないといけません。

この点を検証するために、ユニバーサル基板に手配線で評価用基板を作ってみました。Timpyシリーズで使い慣れたSiLabsの8ビットマイコンC8051とFPGAの組み合わせで構成しました。

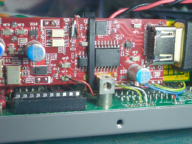

|

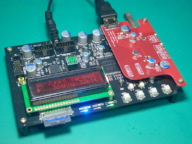

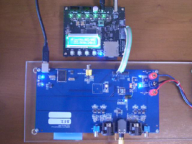

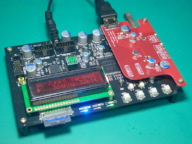

動作しました

Wolfson Microelectronics製WM8741評価ボードと接続しての動作確認の様子です。

|

|

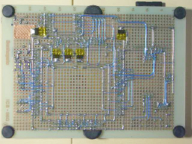

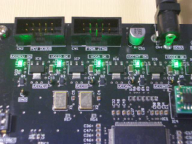

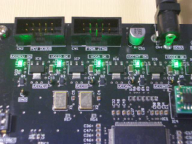

部品面

主な構成部品は以下の通りです。

・マイコン:C8051F361(Silicon Laboratories)

・FPGA:CycloneIII(Altera)

・S/PDIFトランスミッタ:CS8406(Cirrus Logic)

・TCXO:FXO-HC735-24.5760、FXO-HC735-22.5792(Fox Electronics)

|

|

はんだ面

こういう微妙な目的で、かつ高速なデバイスを載せた回路がユニバーサル基板でちゃんと動くのか、ずっと気がかりでした。なので部品配置や電源・グランドの引き回しの検討にはかなりの時間を割きました。

結局、配線のほとんどは電源とグランドになってしまいました。信号のための配線はおそらく半分もありません。回路図を書く必要が無かったくらいですから(実際、ピンアサインをリストしたメモが1枚あるだけです)。

電源はリニアレギュレータで5系統載っています。マイコンとSDカード用の3.3V、TCXOとFPGA用の3.3V、2.5V、1.2V、S/PDIF用の3.3Vです。SDカードは消費電流の変動が大きいので要注意です。

|

動作確認の結果、カードからのデータ転送は問題なく実現できることがわかりました。

手配線ではありますが、音質面でも存外に良い評価をいただくことができました。

この結果を受けて、次のRev2.0を作ることにしました。

★現在このRev1.0基板は、あるオーディオ機器メーカの代表取締役の方が所有されています。

》Rev2.0 : 操作性の向上とプリント基板化

前作Rev1.0において、SDカード・トランスポートの優位性が見えてきました。

そこで液晶パネルやボタンの追加など、マンマシンインターフェースに改良を加えて、プリント基板化してみました。

|

基板化しました

基板設計CADはいつもどおりのEAGLEです。

寸法120mm×100mmの4層板です。今回は黒レジストにしてみました。

面実装部品がほとんどですが全て手はんだです。

こういうはんだ付けって実に難しく、また楽しい作業です。

|

|

液晶ディスプレイと操作スイッチ

液晶ディスプレイはシンプルに、秋月の16文字×2行表示LCDモジュールです。

その下に4個の操作スイッチを配置しました。

右下にLEDが2個あり、SDカードアクセス(青)とFIFOエンプティ(赤)を表示します。

|

|

電源とTCXO

基板の電源入力はDC5V単一です。そこからRev1.0と同様に5系統の電源を作っています。それぞれに緑のモニタLEDを付けました。

写真のやや左下に2つ並んでいるのがTCXO(温度補償型クリスタルオシレータ)です。ひとつは発振周波数24.5760MHzで32KHz系列のサンプルレート時のマスタクロック用、もうひとつは22.5792MHzで44.1KHz系列用です。クロックの切り替えはFPGA内で、altclkctrlメガファンクションにより行っています。

|

|

FPGAとマイコン

液晶の下から半分顔を出しているのがFPGA(上の大きい方)とマイコン(下の小さい方)です。

マイコンはSiLabsのC8051F361です。SiLabsのC8051シリーズは8051互換のCISC型MCUファミリで、パッケージサイズのわりに豊富なペリフェラルを持つ便利なマイコンです。特にこのF36xシリーズは24.5MHzのクロックとPLLを内蔵しており、外付け部品が無くても約100MIPSのピーク性能を発揮します。今回はこのマイコンの性能に頼るところが大きいです。

一方のFPGAはAlteraのCycloneIIIです。SDカードから読み出したデータをバッファリングして、マイコンからの指示に基づき所定のI2S信号として出力します。

|

|

I2S出力とI2Cインターフェース

I2S出力用の8ピン・ヘッダと、I2Cインターフェース用の4ピン・ヘッダです。

"I2S"はディジタル・オーディオ信号規格のひとつです。

I2S規格についてはこちらへ。 I2S規格についてはこちらへ。

ディジタル・オーディオ用LSIはI2CかSPIにより外部制御できるものが多いです。マイコンのSPIポートはSDカードアクセスでいっぱいいっぱいなので、周辺LSI制御はI2Cが担当しています。SPIと違ってバス構成にできる点も柔軟性があっていいですね。現在のファームウェアではS/PDIFトランスミッタであるCS8406の制御と、WM8741評価ボード用のレジスタ設定を行っています。

|

|

S/PDIF出力

もうひとつのオーディオ出力はS/PDIFです。トランスミッタにはCirrus LogicのCS8406を使いました。75ΩのBNCで出力します。

Channel StatusはRIFF WAVファイルヘッダ情報に基づいて、民生用の42ビット分を設定しています。WM8741評価ボードのS/PDIFトランシーバWM8804をソフトウェア制御モードに改造し、受信したChannel

StatusをI2C経由で読み出して、設定どおり出力されていることを確認しました。

|

2009年12月、ファームウェアとFPGAの改良により、192KHz以下なら32ビットまで、24ビットなら352.8KHzまで再生できるようになりました。これにより、"SDTrans192"という名称と実体が合わないという、うれしい誤算となりました。

》Rev2.1 : 音質向上をねらってアートワーク変更

前作Rev2.0での経験から、基板上のディジタル信号のアナログ的振る舞いが音にどのように影響するのかについて、試してみたいことがいくつか出てきました。

そこで、回路はほとんどそのままに、基板設計を見直してみました。

|

改版しました

Rev2.0でのみなさんのご意見をもとに、さらに良い音を目指して改版しました。

|

|

変更の証し

主な変更点がアートワークなので、ちょっと見ただけでは違いがわからないかもしれません。

でもちゃんと、この通り。

|

|

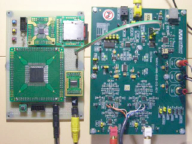

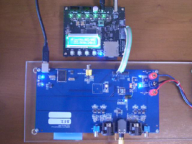

ES9018と共に

ESS Technology社の高性能DAC、ES9018が搭載された評価ボードをお借りすることができました。

352.8KHz24ビットという途方もないオーディオデータを再生しているところです。

|

*SDカードからの高速データ転送

2009年12月リリースのFPGAおよびファームウェアのバージョンから、サンプリングレート352.8KHz、ワードサイズ24ビットのファイル再生が可能となりました。テスト音源は 2LのDXDファイル(中身はWAVファイル)、DACは上記のESS Technology社ES9018評価ボードです。

2LのDXDファイル(中身はWAVファイル)、DACは上記のESS Technology社ES9018評価ボードです。

この場合のWAVデータ転送レートは352,800[Hz]×24[bit]×2[ch]=16,934,400[bps]にもなります。独特の回路構成と100MIPSのC8051パワー、アセンブラを駆使したファームウェアにより実現できました。この時のマイコンの稼働率はおよそ76%です。残る約24%でFAT処理(クラスタチェーン追跡)やマンマシンインターフェース処理などを行っています。FPGAに内蔵したFIFOの容量に対して、まだ十分なマージンが確保できています。

*果たして気になる音質は・・・

Rev2.0と回路的には大きな差異がないにも関わらず、聴き比べたみなさまから『明らかに良くなった』との評価をいただくことができました。考え方としては間違ってないことが確認できました。

★Bunpeiさんのご尽力により、これまでにRev2.0、Rev2.1合わせて20枚以上を国内外のみなさまにお譲りしました。

》Rev3.0 : 全面的な見直しと機能追加

Rev2.0とRev2.1の間で変えたことは、アートワークの設計思想です。回路的にはほとんど変わっていません。でもそれにより、明らかな音質改善効果を得ることができました。

当然、『この考え方をもっと強力に推し進めてみたら…?』という興味がわいてきます。そこで、回路とアートワークの両方について、全面的な見直しを図ってみました。同時に新機能として、リモート入出力や、I2S信号のLVDS出力なども盛り込みました。

|

外観

Rev2.1と比べて横幅が少し長く、100mm×160mmになりました。液晶は黒地に赤文字。I2S信号をLVDSで出力するためのHDMIコネクタが追加になっています。

|

*Rev2.1からの主な変更点

・新しい設計思想に基づく、改良型新基板

・クロック、電源まわりを中心に、回路を全面的に見直し

・マスタクロック用オシレータモジュールをNDK製超低ジッタ型に変更

・外部機器から本機の動作を制御したり、LEDの状態をモニタしたりするためのリモートI/Oを追加

・PS-Audio相当のLVDSによるI2S出力を追加

・外部クロック入力端子を追加

・外部電源供給端子を追加

・液晶モジュールを構造的に強固なタイプに変更

・液晶モジュールのバックライトLED制御端子を追加

・制御用マイコンをプログラムメモリの大きなものに変更

|

すてきな贈り物

Rev3.0ユーザのY氏から、専用の木製シャーシとアクリルパネルをいただきました。実にきれいな仕上がりで、基板むき出しの無粋な外観を、見事に変身させてくれる逸品です。Yさん、どうもありがとうございました。

|

*果たして気になる音質は・・・

マスタクロック源として新たに採用したNDK製超低ジッタ型オシレータの威力とあいまって、非常に良い評価を得ることができました。

オーディオ名機賞2011を受賞したFidelix社製Capriceの開発に際してもお役に立てたようです。

*ES9018との同期化 【2011年7月2日 追記】

話題の高性能DACチップES9018とSDTrans384の組み合わせで、簡単な実験をしてみましたのでご紹介します。

ES9018では、トランスポートからマスタクロックを供給する必要がありません。ES9018に内蔵されたDPLLがマスタクロックとして機能します。また、入力されるオーディオ信号はこのマスタクロックと同期している必要もありません。逆に非同期であることを利用して、オーディオ信号に含まれるジッタを除去できることが特徴のひとつになっています。

このDPLLに関する設定において、"DPLL Bandwidth"が"Lowest"に近いほど聴感上好ましいのは異論の無いところでしょう。しかしながら、そうするとDPLLのロックが外れやすくなり、実用に耐えません。特にI2Sの場合、およびサンプルレートが高いほど、その傾向は強くなります。DPLLもPLLの一種でしょうから、その動作を推測するに、SDTrans384とES9018を同一のクロックで動作させれば改善される可能性が考えられます。そこで、SDTrans384に搭載されているNDKのクロックをFPGAのPLLを使って4逓倍し、ES9018に供給してみました。

その結果、I2S接続の44.1KHz〜384KHz全てにおいて、"Lowest"設定でもDPLLのロックが外れなくなりました。また複数の方の試聴により、聴感上でも明らかに向上しているとの評価になりました。これは、DPLLの追従による時間軸上の変動が最小限になった(つまりLowestより小さい)ためと思われます。(非公開情報の開示になるおそれがありますのでここまでにしておきます。本当はいろいろと書きたいことがあるのですが・・・)

同期化に伴い、供給するクロックの質が非常に重要となりますが、SDTrans384側のPLLで生成したクロックでも効果は十分にあるようです。

この実験はSDTrans384とESS社純正のES9018評価ボードの組み合わせで行いました。またBunpeiさんにより、BuffaloIIとの組み合わせでも動作が確認されています。接続はいずれもI2Sです。S/PDIFとDSDでも有効かもしれませんが未確認です。

同期クロックとしては、SDTrans384のCN8から出力されているMCLK、またはCN3のLVDS経由で外部生成されたMCLKが利用できます。

メールでお問い合わせがありましたので実験方法をご紹介します。実験にはSDTrans384とDACの両方に改造が必要です。

(1)SDTrans384基板上のJP6をJP5に移す(CN8経由の場合)、またはJP2をJP1に移す(CN3経由の場合)

(2)DAC側のオシレータを取り外す

(3)DACのクロックラインに、SDTrans384のCN8のMCLK信号、またはCN3経由で外部生成されたMCLK信号を接続する

(4)SDTrans384のコンフィグROMを17aのものに交換する

以上です。さらっと書いてありますが難易度は高めかも知れません。この改造に関して私は一切の責任を負いません。

*Capriceとの同期化 【2011年7月24日 追記】

SDTrans384のクロックをES9018に供給して同期化するという上記の試行を、Fidelix社製Caprice(I2Sオプション付き)に適用してみました。その結果、44.1KHz〜384KHzの全てにおいて、Lowest設定でもロック外れすることなく再生できるようになりました。

【ご注意】

SDTrans384ユーザのXさんから、Caprice-I2Sオプション基板には、搭載されているアイソレータチップにより複数のバージョンが存在するとの情報をいただきました。私のものにはTIのISO7240Mが載っています。使用ICや回路が異なる場合には同様の動作にならないおそれがあります。いずれにしましてもこれは「改造」ですので、ご自身の責任においてお願いします。この件に関してFiderix社のご迷惑となる行為はご遠慮ください。(情報を提供してくださったXさん、ありがとうございました)

*SDTrans384に名称変更

ファームウェア3.10、FPGA016にて、384KHz32ビットの再生に対応しました。これを記念して、以降名称を"SDTrans384"とすることにしました。

基板のシルク文字は"SDTrans192 Rev3.0"のままですけど。(^^;;

★更新日時点で、トランスポート本体としては、このSDTrans192 Rev3.0 (SDTrans384)が最新作です。

★最新版ファームウェアは3.16、FPGAが023です。

Rev3.0旧版からのアップデートをご希望の方は、直接メールにてお問い合わせください。

★PCM(I2S)に加えて、DSDIFF(DSD64、DSD128、DSD256)の再生にも対応しました。

MCLKには標準設定ならきれいな20MHz系クロックが出力されます。ジャンパを変更すればPLLで生成した90MHz系も出力可能です(ジャンパは1608サイズのチップ抵抗です)。

★DSD再生開始時・停止時のプチノイズを実用上問題ない程度まで解消しました。

DSDモードでも、PCMモード時と同様にソフトミュートします。

この実装はとても難しい作業でした。

特に次の2点が難問でした。

(1)きれいなフェード動作

DSDのビットストリームに対して、十分に低ノイズなフェード演算を加えてDSDとして出力することは、PCMのように簡単にはいきません。単純な数値演算で済むようなデータ形式ではないからです。

(2)プチノイズの無い、なめらかな状態遷移

ひとつの例ですが、例えば0x55の連続、および0xAAの連続はそれぞれ無音となります。でもその2つの連続データを単に連結させると、つまり0x55,

0x55, …, 0x55, 0xAA, 0xAA, …, 0xAAとすると、その境目で盛大にプチノイズが出ます。

ミュートしていない時の出力データは、ファイルデータそのままでなければなりません(ビットパーフェクト)。それを保証しつつ、さらにプチノイズの発生も抑えながら、なめらかにフェードイン/フェードアウトさせることは想像以上に大変でした。

》Rev3.0+Syncオプション : DACをクロックマスタに

DACチップに供給されるマスタクロックの質は、音の良し悪しを左右する最重要項目のひとつです。

トランスポートとDACの同期化が有効であることは、前項の試行で確認できました。しかしながら、同期クロックをトランスポートからDACへ送るのは、最重要項目であるクロックの質の確保において不利であることは間違いありません。

そこで、DAC側にマスタクロック源を配置し、かつトランスポートと同期化できるようにするためのSDTrans384用オプション基板を作ってみました。

*基板構成

このSyncオプションは、“SDTrans384-Sync-SDT”と“SDTrans384-Sync-DAC”という真っ赤な2枚の基板で構成されます。それぞれ名前が長すぎ(汗)なので、以後“Sync-SDT基板”、“Sync-DAC基板”と呼ぶことにします。

Sync-SDTはSDTrans384へのアドオン基板です。Sync-DACはDAC側に組み込むことになる基板です。

*マスタクロック

マスタクロック用オシレータはSync-DAC基板に搭載されています。NDK製超低ジッタ型の特注品で、44.1KHz系用の90.3168MHzと、48KHz系用の98.3040MHzの2個を使用しました。この2個は、SDTrans384側から曲のサンプルレートに従って切り替えられます。

*接続形態

Sync-DAC基板とSync-SDT基板の間は、PS-Audioと同様にHDMIケーブルの流用にて接続できるようにしました。オシレータで生成したマスタクロックは、DAC内でES9018に供給されると共に、HDMIケーブルを通してSDTrans384側にも送られます。SDTrans384は、このクロックを受けて、同期したオーディオデータをDACへと送出します。つまりこのSyncオプション方式では、オリジナルのPS-Audio方式に対して、MCLK信号だけ伝送方向が逆になっている点に注意してください。勝手ながら私はこれを"SDTrans-Sync方式"と呼んでいます。

*SDTrans384側からのDAC制御

HDMIケーブルにはI2C信号も通すことができるので大変好都合です。Syncオプションでは、2個のオシレータの切り替え制御の他、ES9018のレジスタ設定や、I2S/DSD切り替え制御もHDMI経由のI2Cにて制御しています。これにより、DACとSDTrans384間の接続はHDMIケーブル1本だけでOKです。

*アイソレート

SDTrans384側からのノイズ伝播を抑えるため、Sync-DAC基板上にデジタルアイソレータを搭載しました。マスタクロック、I2S/DSD、I2C、電源に至るまで、全てを電気的に絶縁してあります。またオシレータなどのためのSync-DAC基板用電源は、DAC本体とは別に、外部から電池などで供給できるようにしました。

★このSyncオプションに採用したオシレータが大変高価(SDTrans384搭載品の10倍以上!)なため、SDTrans384本体より費用がかかってしまいました。orz

★Sync基板製作後、後追いでDSD再生にも対応しました。DSDIFFの2.8MHz(44.1KHz系DSD64)、3.1MHz(48KHz系DSD64)、5.6MHz(44.1KHz系DSD128)、6.1MHz(48KHz系DSD128)、11.3M(44.1KHz系DSD256)、12.3M(48KHz系DSD256)をサポートします。WAVファイルとDFFファイルの両方に自動対応します。

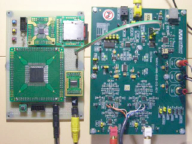

|

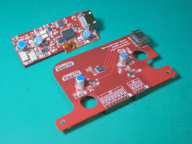

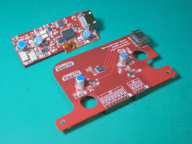

SDTrans384-Sync Rev1.0 オプション基板

左上の小さい方がSync-DAC基板で、大きい方がSync-SDT基板です。

今回は気分を変えて赤にしてみました。

LVDS、LVPECLのラインはインピーダンス制御してあります。

実装は相変わらずの手はんだです。

|

|

SDTrans384への組み付け

Sync-SDT基板は、SDTrans384本体にスタックされる形で組み付けます。

|

|

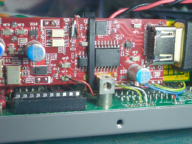

DACへの組み込み

写真はCapriceを改造して組み込んだ例です。

このSyncオプションを経由してES9018のレジスタ設定も行っています。そのため、Capriceに標準搭載のマイコンは取り外しました。左下の黒い部分が空になったICソケットです。リモコンとか入力切替は使用していないので、私的には問題ありません。(^^;;

|

|

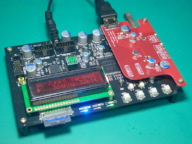

動作中…

最近対応したDSD128ファイルを再生しているところです。

SDTrans384とDAC側Syncオプション共に、電池で十分動作します。

|

*果たして気になる音質は・・・

○PCM(I2S)について

・Bunpeiさんからいただいた掲示板へのコメント:『一言「素晴らしい」につきます。最近SDTransとBuffalo IIの同期の接続で、Buffalo II側の電源を改良することでかなり良くなることを確認していたのですが、それよりもさらに良くなっているように感じております。…』。また、『それほど真剣に聴かなくても、音の出だしから「おっ」と感じられる』との感想をいただきました。

・Lyra社のJonathan Carr氏からは、diy Audio forumにて大変良い評価のコメントを寄せてくださいました。

・あるオーディオ機器メーカの方からは、『音質的にはしばらくの間、もうこれで十分』とのお言葉をいただきました。

・掲示板にて、tetuさんから、Capriceとの組み合わせでの詳細かつ高評価のコメントをいただきました。

…などなど、この上なくうれしい結果となりました。

○DSDについて

・Bunpeiさんからいただいた掲示板へのコメント:『CDからリッピングしたソース、DSDのソース、DXDなどのハイレゾソースがいずれもこれまでも聴いたよりもすべて点で良く聴こえます。私の言葉で表現すると「精密かつ音楽的な音」です。CDからリッピングしたソースをAudioGateでDSD128に変換したものを聴くとその違いが認識できました。』

・eleconさんが、diy Audio forumにて大変良い評価のコメントを寄せてくださいました。

…などなど、DSDについてもとてもうれしい結果が得られました。

★最新版ファームウェアは3.22、FPGAは022です。

★Syncオプションの頒布は終了しました。ありがとうございました。

》SDTrans-Sync-9018D : SDTrans-Sync方式デュアルモノDAC

Syncオプションと同じSDTrans-Sync方式を採りつつ、ES9018のデュアルモノ構成が楽しめるDAC基板を作ってみました。

前作Syncオプションの最大の特徴は、DAC側にマスタクロック源を配置し、トランスポートはクロックスレーブとして同期動作する構成(=SDTrans-Sync方式)です。でもSyncオプション基板を使ってES9018のデュアルモノ構成を考えようとすると、トランスポートとDACが双方向に信号をやり取りしていることもあって、回路的に難しい部分がありました。

そこで今回製作したのは、SDTrans-Sync方式とES9018デュアルモノ構成を両立させることができるDAC基板です。

主な特徴は以下の通りです。

・ES9018を2個使用したデュアルモノ構成

・ES9018の電流出力をそのまま差動出力(I/V回路は非搭載)

・Syncオプション(Sync-SDT基板)を追加したSDTrans384との組み合わせで動作し、必要なケーブルはHDMIケーブル1本のみ

・マスタクロック源として、Crystekの最新型超低位相ノイズオシレータCCHD-957シリーズ(45.1584MHz、49.152MHz)を採用

・10個の超低ノイズリニアレギュレータを搭載(外部供給も可能)、5系統の5V電源で動作

・トランスポート側回路とDAC側回路は電気的に絶縁

・SDTrans-Sync方式による完全同期動作(常時Lowest設定、ロック外れ無し)

・PCM/DSDをシームレスに再生可能

この基板では試行の意味も含めて、Crystekの新製品を採用してみました。周波数が40MHz台と低めなので、352.8KHzと384KHzのPCM再生時に限りOSFをオフに設定しています。

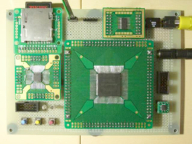

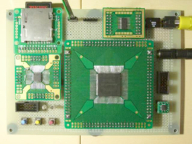

|

SDTrans-Sync-9018D Rev1.0 基板

基板寸法は100mm×105mmとかなり小さいです。

実はこの基板、常識破りともいえる禁じ手が使われています。わかります?

|

|

動作中…

SDTrans384側からの制御により、PCMファイルとDSDファイルを区別無く再生できます。1枚のカードにいろんなフォーマットのファイルを混在させても全く問題ありません。

写真は12.3MHz(48KHz系)DSD256ファイルを再生しているところです。

|

|

高層化…?

いつまでも電池駆動というわけにもいかないので、電源を用意して組み上げてみました。

なんか高層マンションのよう・・・(汗)。

最上階はSDTrans384+Sync-SDT、その下はSDTrans-Sync-9018Dです。さらにその下に3個×2階分=6個並んでいるのはAC/DCリニア電源です。それも6個全て5V出力・・・。SDTrans-Sync-9018D用に5個、SDTrans384+Sync-SDT用に1個です。

最下層は動作確認用のI/V基板と、±15V出力の電源がL/R用各1個ずつとなっています。

|

》SDTrans-9018D-IV : SDTrans-Sync-9018D用 IV変換基板

ES9018の8出力を1本にまとめた電流出力を、電圧出力に変換するための基板です。

電圧出力でのひとつのリファレンスを目指して、ES9018のメーカ推奨回路を採用しました。

同時に、全てスルホール部品で統一することで、回路や使用部品、部品定数の変更・改造などがしやすい設計になっています。

主な特徴は以下の通りです。

・SDTrans-Sync-9018D基板にスタック可

・LR完全独立構成

・I/V段はES9018推奨回路をほぼそのまま採用

・使用部品は全てスルホール品

・SDTrans384から9018D基板を経由して制御されるミュート回路を搭載

・出力はバランス、アンバランス共に可能

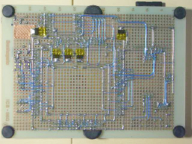

|

SDTrans-9018D-IV Rev1.0 基板

今回の基板は青色です。

面実装部品を使わないようにしたら、思いのほか実装密度が高くなってしまいました。

|

|

DACとの接続

SDTrans-Sync-9018D(写真下側の基板)上にスタックできるように設計しました。

|

|

SDTrans384 + Sync-SDT + Sync-9018D + 9018D-IV

IV基板完成に伴い、全体をを組み替えました。

・トランスポート : SDTrans384+Sync-SDT

・DAC : SDTrans-Sync-9018D

・IV : SDTrans-9018D-IV

です。

8個の黒いブロックはAC/DCリニア電源です。

|

Copyright 2009-2012 Chiaki Nakajima.

All rights reserved.

![]()

![]()

![]()

![]()

![]()

![]()

![]()